# Field Engineering Maintenance Manual

# www.IBM360.info

2055 Processing Unit

# **Preface**

This manual, Form Y27-2270-0, is a completely revised edition of the maintenance manual for the 2065 Processing Unit and obsoletes the previous edition, Form Y27-2039-1. The following CE memorandum service aids (SA's) have been incorporated into this manual:

| SA Category | SA No.                              |

|-------------|-------------------------------------|

| ROS         | A1,A2,A3,A4,A6,A7,A8,A9,A11,A13,A14 |

| DIAG        | A7,A8,A9,A10,A11,A12,A13,A14,E3     |

| PWR         | 5,11,12                             |

| GEN         | 11,12                               |

The information in this manual is presented in six chapters: Chapter 1 contains reference data; Chapter 2 describes operating procedures, maintenance features, and diagnostic programs; Chapter 3 contains preventive maintenance information; Chapter 4 contains maintenance

procedures and service aids which are to be used in conjunction with the diagnostic techniques diagrams (category 1) in the 2065 FEMDM (Form Y27-2038-0); Chapter 5 contains power supply maintenance information; and Chapter 6 identifies frame locations.

Companion and prerequisite manuals to the 2065 FEMM are:

2065 Processing Unit, FETOM (Volume 1), Form Y27-2036-0

2065 Processing Unit, FETOM (Volume 2), Form Y27-2037-0

2065 Processing Unit, FEMDM, Form Y27-2038-0

It is assumed that the reader has been trained on the 2065 and that he is familiar with ALD interpretation and the use of oscilloscope and related tools.

# First Edition (October, 1969)

Information in this manual is subject to change from time to time. Any such change will be reported in subsequent revisions or FE Supplements.

Text for this manual has been prepared with the IBM SELECTRIC ® Composer.

A form is provided at the back of this publication for reader's comments. If the form has been removed, comments may be addressed to: IBM Systems Development Division, Product Publications, Dept 520, Neighborhood Road, Bldg. 960-1, Kingston, N.Y., 12401.

©Copyright International Business Machines Corporation, 1969

# Contents

| Chapter 1.     | Reference Data 1-1                                       | 2.23       | Store Doubleword into Main Storage 2-8           |

|----------------|----------------------------------------------------------|------------|--------------------------------------------------|

| 1.1            | Data Flow and Control 1-1                                | 2.24       | Store Single Byte into Main Storage 2-8          |

| 1.2            | System Coding 1-1                                        | 2.25       | Display CAW 2-8                                  |

| 1.2.1          | Hexadecimal/Decimal Conversion 1-1                       | 2.26       | Store CAW                                        |

| 1.2.2          | Eight-Bit Zoned Character Codes (USASCII-8               | 2.27       |                                                  |

| 1.2.2          | ·                                                        |            | Display CCW 2-9                                  |

| 1.0.0          | and EBCDIC) 1-3                                          | 2.28       | Store CCW                                        |

| 1.2.3          | Instructions and Instruction Formats 1-5                 | 2.29       | Clear Storage Procedure 2-9                      |

| 1.2.4          | Data Formats 1-5                                         |            |                                                  |

| 1.3            | Program Status Words (PSW) 1-23                          |            |                                                  |

| 1.4            | I/O Control Words 1-23                                   | SECTION 3. | MAINTENIANCE DE ATTIDEC 2.10                     |

| 1.5            | Logic Diagrams 1-25                                      |            | MAINTENANCE FEATURES 2-10                        |

| 1.5.1          | ALD Notation                                             | 2.30       | Diagnose Instruction and MCW's 2-10              |

| 1.5.2          | Additive Card Codes 1-25                                 | 2.30.1     | Diagnose Instruction MCW for CPU 2-11            |

|                |                                                          | 2.30.2     | Diagnose Instruction MCW for Channel 2-11        |

| 1.5.3          | ALD Index 1-26                                           | 2.30.3     | ROS Test MCW 1-12                                |

| 1.5.4          | CLD Notation                                             | 2.30.4     | FLT MCW 2-12                                     |

| 1.5.5          | CLD Index                                                | 2.31       | Scan-In Operations 2-12                          |

| 1.5.6          | Version Numbers 1-30                                     | 2.31.1     | Conditions for Scan-In Using Diagnose            |

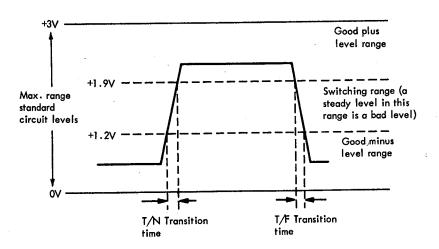

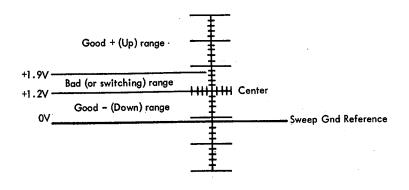

| 1.6            | Model 65 Circuit Levels 1-30                             | 2.31.1     | Instruction 2-13                                 |

| 1.7            | Sync Signals and Locations 1-31                          | 0.01.0     |                                                  |

| ,              | 2,100 2.5.00.00 2.00.00.00 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 2.31.2     | Reference Data for Scan-In Facilities 2-13       |

| Chapter 2.     | Console and Maintenance Features 2-1                     | 2.31.3     | Scan-In Program Examples 2-13                    |

| Chapter 2.     | Console and Maintenance Features 2-1                     | 2.32       | Logout, ROS Tests, and FLT's 2-15                |

| 675.67T.63.T.4 |                                                          | 2.32.1     | Logout                                           |

| SECTION 1.     | CONTROL PANELS 2-1                                       | 2.32.2     | ROS Tests                                        |

| 2.1            | System Control Panel 2-1                                 | 2.32.3     | FLT's                                            |

| 2.1.1          | Panel A                                                  | 2.32.3.1   | Hardcore Tests                                   |

| 2.1.2          | Panel B                                                  | 2.32.3.1   |                                                  |

| 2.1.3          | Panel C                                                  |            | Zero-Cycle Tests                                 |

| 2.1.4          | Panel D                                                  | 3.32.3.3   | One-Cycle Tests                                  |

| 2.1.5          | Panel E                                                  | 2.33       | Diagnostic Programs                              |

| 2.1.6          | Panel F                                                  | 2.33.1     | Hard Core                                        |

| 2.1.7          | Panel G                                                  | 2.33.2     | Diagnostic Monitor E (DME) 2-20                  |

| 2.1.7          |                                                          | 2.33.3     | Machine Check Analysis 2-20                      |

|                |                                                          | 2.33.4     | Interrupt Test                                   |

| 2.3            | Configuration Control Panel (Multisystem                 | 2,33.5     | CPU Error Detection and Analysis (CEDA) . 2-22   |

|                | Feature Only) 2-4                                        | 2.33.5.1   | Instruction Isolation 2-22                       |

| 2.3.1          | Storage Allocation Switches 2-4                          | 2.33.5.2   | CLD Isolation 2-22                               |

| 2.3.2          | Floating Address Switches 2-4                            | 2.33.5.3   | Program Micro-Trace 2-23                         |

| 2.3.3          | PREFIX Switches 2-5                                      | 2.33.5.4   | Extended Print and Error Utility 2-23            |

| 2.3.4          | CPU Mode Switches 2-5                                    | 2.33.6     | Model 65 Logout                                  |

| 2.3.5          | I/O Allocation Switches 2-5                              | 2.33.7     |                                                  |

| 2.3.6          | VALID ADDRESS Indicators 2-5                             | 2.33.8     | Diagnose Test                                    |

|                |                                                          |            | Storage Diagnostic                               |

| SECTION 2.     | CONSOLE OPERATING PROCEDURES 2-6                         | 2.33.9     | Intermittent Storage Error Detection 2-25        |

| 2.4            | Turning On System Power 2-6                              | 2.33.10    | Storage Protect Test 2-25                        |

| 2.5            |                                                          | 2.33.11    | Channel Programs 2-26                            |

|                | Turning Off System Power 2-6                             | 2.33.12    | System Interrogation Program (SIP) 2-26          |

| 2.6            | Stopping and Restarting the System 2-6                   | 2.33.13    | System Error Recording and Editing 2-26          |

| 2.7            | Resetting the System 2-6                                 | 2.33.13.1  | Recording Programs 2-26                          |

| 2.8            | Resetting CPU Error Check Logic 2-6                      | 2.33.13.2  | Editing Programs 2-26                            |

| 2.9            | Emergency Power Off 2-6                                  | 2.33.14    | Diagnostic Sections (Emulator Features) 2-26     |

| 2.10           | Turning On Control Unit Power 2-6                        | 2.33.14.1  | 7074 Emulator Diagnostics 2-27                   |

| 2.11           | Turning Off Control Unit Power 2-6                       | 2.33.14.2  | 7080 Emulator Diagnostics 2-27                   |

| 2.12           | Manual IPL                                               | 2.33.14.3  | 7090 Emulator Diagnostics 2-27                   |

| 2.13           | Display PSW 2-7                                          | 2.33.15    |                                                  |

| 2.14           | Restart from Initial PSW 2-7                             | 4.33.13    | Diagnostic Sections (Multisystem Feature) . 2-27 |

| 2.15           | Load Instruction Counter                                 |            |                                                  |

| 2.16           | Instruction Stepping 2-7                                 |            |                                                  |

| 2.17           |                                                          |            |                                                  |

| 2.17           | Display LS General Register                              | Chapter 3. | Preventive Maintenance                           |

|                | Load LS General Register                                 | -improi O. |                                                  |

| 2.19           | Display LS Floating-Point Register 2-8                   | SECTION 1  | BASIC UNIT                                       |

| 2.20           | Load LS Floating-Point Register 2-8                      | SECTION I. | DAGIC UNIT                                       |

| 2.21           | Address-Compare Stop Procedure 2-8                       | CECTION C  | EE A TELIDEO                                     |

| 2.22           | Display Doubleword from Main Storage 2-8                 | SECTION 2. | FEATURES                                         |

| Chapter 4.         | Maintenance Procedures 4-1             | 4.13.1<br>4.13.2   | Removal                                        |

|--------------------|----------------------------------------|--------------------|------------------------------------------------|

| SECTION 1.         | SERVICE CHECKS AND REPAIR              | 4.13.3             | Installation 4-22                              |

| BECTION 1.         | PROCEDURES 4-1                         | CECTION 4          | GEDVICE AIDG 4.25                              |

| 4.1                | Main Storage Ripple Tests 4-1          | SECTION 4.<br>4.14 | SERVICE AIDS                                   |

| 4.1.1              | Write All 1's                          | 4.14               | Intermittent Processor Checks 4-25             |

| 4.1.2              | Read All 1's                           | 4.16               | Stop-Loop Failures 4-25                        |

| 4.1.3              | Write/Read All 0's 4-1                 | 4.10               | Processor Checks; Determining Failing          |

| 4.1.4              | Write/Read Alternate Pattern 4-1       | 4.17               | ROS Cycle                                      |

| 4.1.5              | No Parity Bit Pattern 4-1              | 4.17               | CPU Troubleshooting Flowcharts 4-26            |

| 4.2                | Local Store Ripple Tests 4-1           |                    | Repetition of Selected ROS Word 4-26           |

| 4.2.1              | Write All 1's                          | 4.19               | Stop on ROS Address Compare 4-28               |

| 4.2.2              | Read All 1's                           | 4.20               | Clearing Wait Bit                              |

| 4.2.3              | Write/Deed All O'c                     | 4.21               | Determining Trigger Being Tested by FLT . 4-28 |

| 4.2.4              | Write/Read All 0's                     | 4.22               | Repetitive Console Pushbutton Operation 4-30   |

| 4.2.5              | Write/Read Alternate Pattern 4-1       | 4.23               | Visual Display of Log Data Indicators 4-30     |

| 4.3                | No Parity Bit Pattern                  | 4.24               | I/O Scoping Loop 4-30                          |

| 4.3.1              | ROS Tests                              | 4.25               | Servicing Techniques Using Oscilloscope 4-31   |

| 4.3.1              | ROS Parity Checking                    | 4.26               | Turning on Check Stop After Hard Core          |

| 4.3.3              | ROS All 0's, All 1's Word Tests        |                    | (601F) Runs 4-31                               |

| 4.3.4              | ROS Word Tests                         | 4.27               | Hints for Running SIP 4-32                     |

| 4.3.4              | ROS Hardcore Repair                    | 4.28               | Analyzing an Unexpected Wait State             |

|                    | ROS Hardware Tests                     |                    | Condition                                      |

| 4.3.6              | ROS Hardware Repair                    | 4.29               | Analyzing I/O Commands 4-32                    |

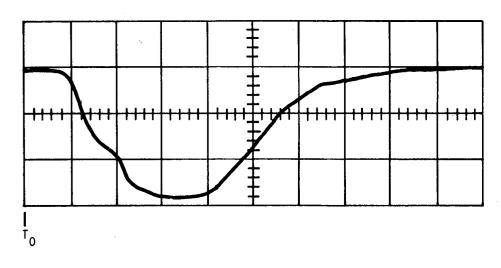

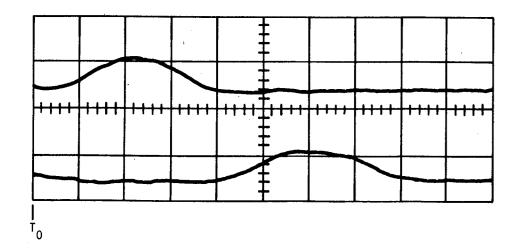

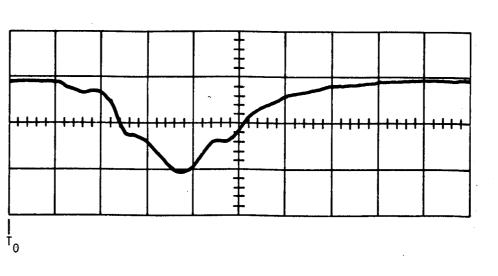

| 4.3.6.1            | Weak Sense Amplifier Output 4-7        | 4.30               | Analyzing Imprecise Interrupts 4-32            |

| 4.3.6.2            | Distorted or Missing Sense Amplifier   | 4.31               | Single Address BCU Scoping Loop 4-33           |

| 4.3.6.3            | Output                                 | Ob                 | D                                              |

| 4.3.6.3.1          |                                        | Chapter 5.         | Power                                          |

| 4.3.6.3.2          | Electrical Noise                       | 5.1                | Visual Inspection and Cleaning 5-1             |

| 4.3.6.3.3          | Troubleshooting Noise Problems 4-9     | 5.2                | Power Checks 5-1                               |

|                    | Late ROS Branching                     | 5.3                | Marginal Checking 5-1                          |

| 4.3.6.3.4          | Multiple Drive Line Selection 4-11     | 5.4                | Voltage Checks and Adjustments 5-1             |

| 4.3.6.4            | Extra Bits (Bit 99 only) 4-11          | 5.4.1              | Regulator Output Voltage Adjustment 5-4        |

| 4.3.6.5            | ROS Parity Checks in Wait State 4-12   | 5.4.2              | Regulator Overvoltage Trip Adjustment 5-4      |

| 4.3.6.6            | Intermittent ROS Failures 4-12         | 5.4.2.1            | Converted Units 5-4                            |

| 4.4                | FLT's                                  |                    | Original Units 5-4                             |

| 4.4.1              | FLT Hardcore Repair 4-12               | 5.4.3              | Regulator Undervoltage Trip Adjustment 5-5     |

| 4.4.2              | FLT Zero-Cycle Tests 4-13              | 5.5                | Troubleshooting 5-5                            |

| 4.4.3              | FLT Zero-Cycle Repair 4-13             | 5.5.1              | Power Supply Protection Circuits 5-5           |

| 4.4.4              | FLT One-Cycle Repair 4-15              | 5.5.1.1            | Circuit Interlocks 5-5                         |

| 4.4.5              | 2065 SCOPEX Timings 4-15               | 5.5.1.2            | Voltage Sensing Circuits 5-5                   |

| 4.5                | Diagnostics 4-16                       | 5.5.1.3            | Current Sensing Circuits 5-6                   |

| 4.6                | Timing Checks 4-16                     | 5.5.1.4            | Thermal Sensing Circuits 5-6                   |

| 4.7                | Lamp Tests 4-16                        | 5.5.2              | Converter/Inverter 5-6                         |

| 4.8                | Signal to Frame Ground Shorts; Service | 5.5.3              | Regulators 5-7                                 |

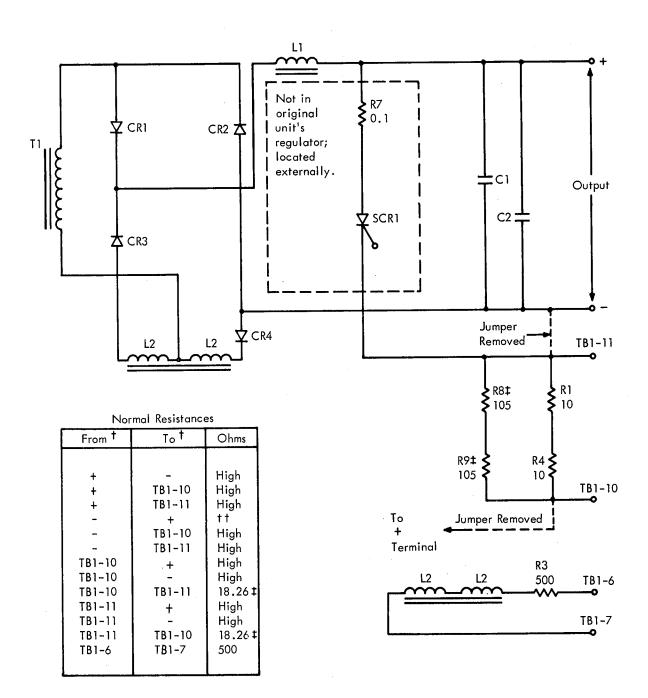

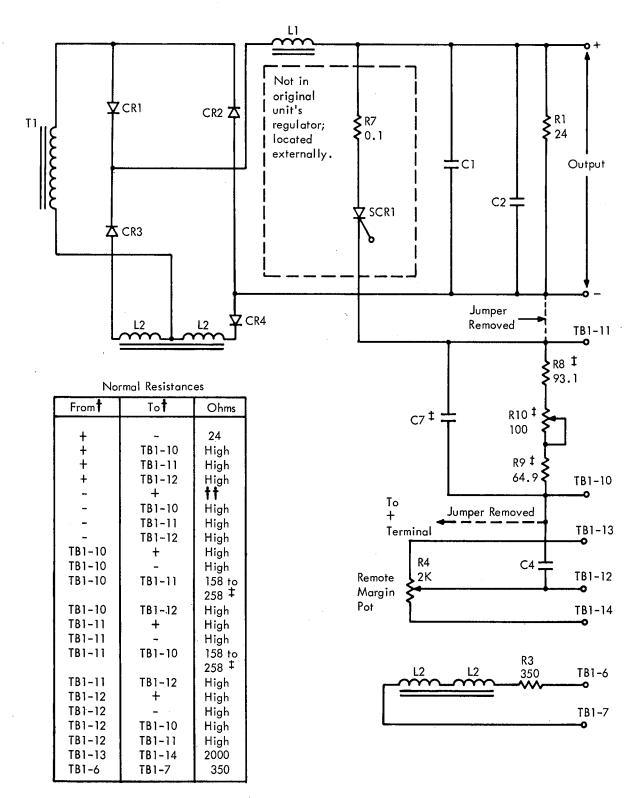

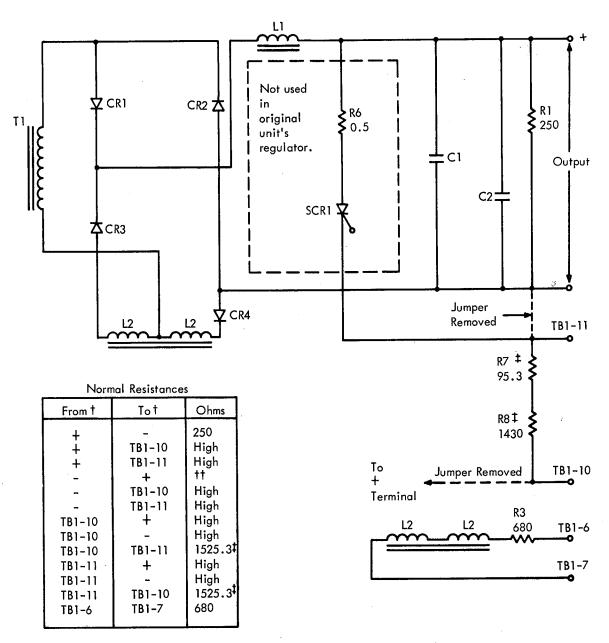

|                    | Check 4-16                             | 5.5.3.1            | SCR Regulator 5-9                              |

|                    |                                        | 5.5.3.2            | Magnetic-Amplifier Regulator 5-10              |

| SECTION 2.         | ADJUSTMENTS 4-18                       | 5.6                | Replacement 5-11                               |

| 4.9                | <b>ROS Optimization</b> 4-18           | 5.6.1              | Converter/Inverter Replacement 5-11            |

| 4.9.1              | Adjustment Procedure 4-18              | 5.6.2              | Regulator Replacement 5-13                     |

| 4.9.2              | Debugging Procedure 4-19               |                    |                                                |

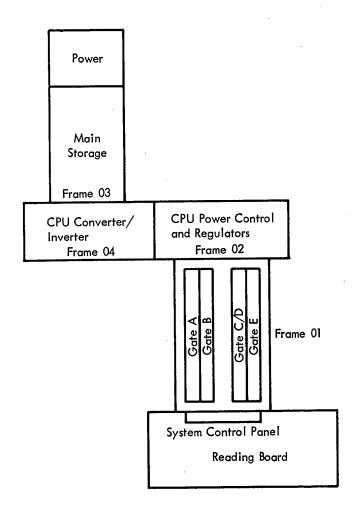

| 4.10               | Elapsed Time Meter Calibration 4-20    | Chapter 6.         | Locations 6-1                                  |

| 4.11               | 1052 Singleshot Adjustment (1052       | •                  |                                                |

|                    | Attachment Feature Only) 4-20          | Appendix A.        | Special Circuits                               |

| SECTION 3.         | DEMOVALS                               | A                  | Walker was 0.19 and 1.00                       |

| SECTION 3.<br>4.12 | REMOVALS                               | Appendix B.        | Voltmeter Calibration Chart B-1                |

| 4.12<br>4.13       | ROS Bit Planes                         | Indos              |                                                |

| 1110               | NOD DILLIANDS 4-22                     | muex               |                                                |

# Illustrations

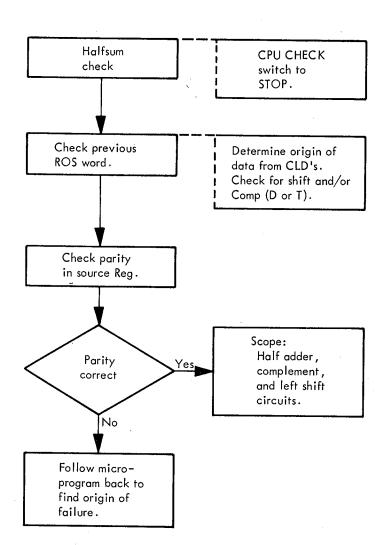

| 1-1  | Powers of 2 and 16                                    | 4-19       | Parallel Adder Half-Sum Check Trouble -        |

|------|-------------------------------------------------------|------------|------------------------------------------------|

| 1-2  | Binary and Hexadecimal Conversion Charts              |            | shooting 4-30                                  |

|      | (2) Parts)                                            | 4-20       | I/O Scoping Loop 4-31                          |

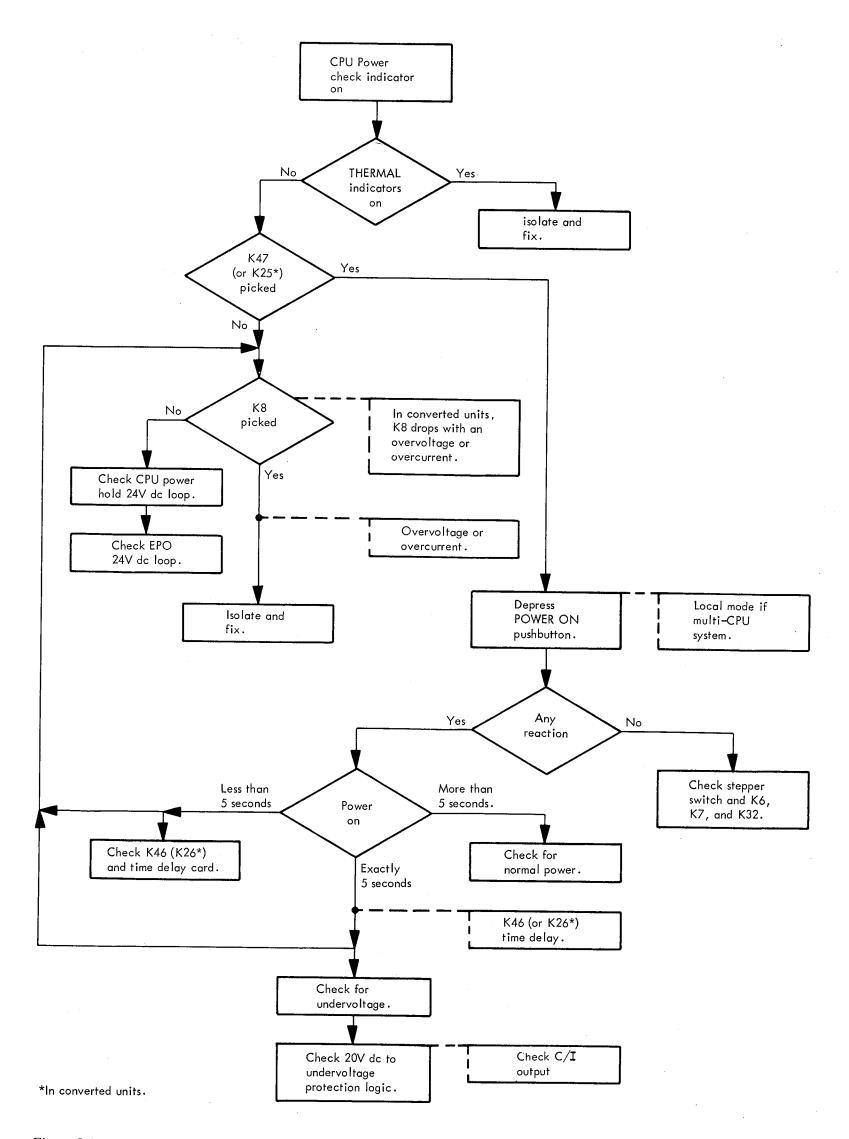

| 1-3  | EBCDIC Code                                           | 5-1        | CPU Power Checkout 5-2                         |

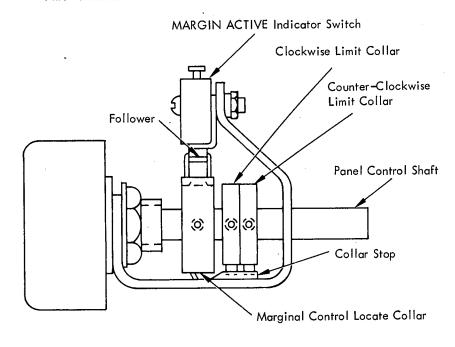

| 1-4  | USASCII-8 Code                                        | 5-2        | Marginal Check Potentiometer Adjustment        |

| 1-5  | Instruction Formats 1-7                               | <b>0 -</b> | Limits                                         |

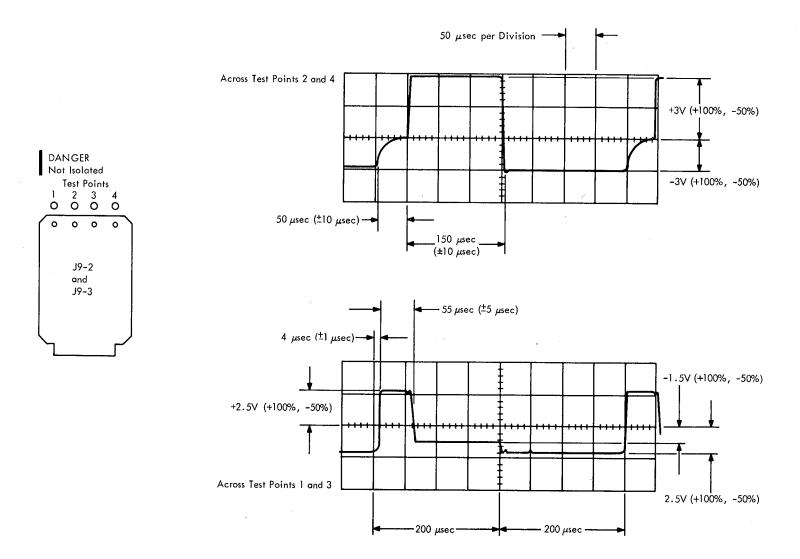

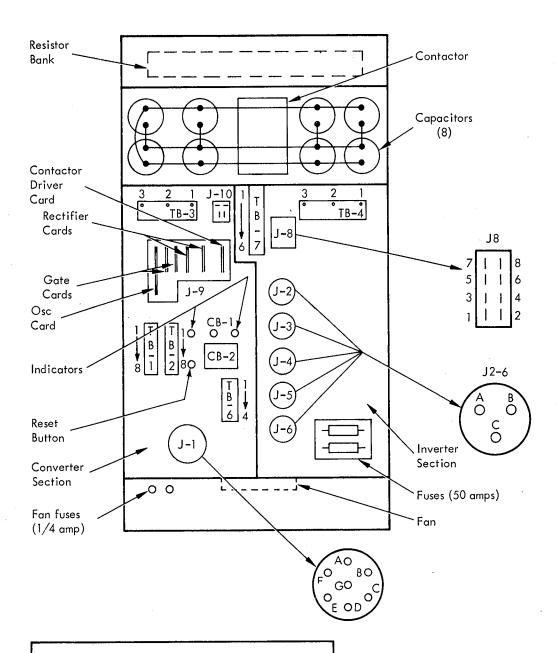

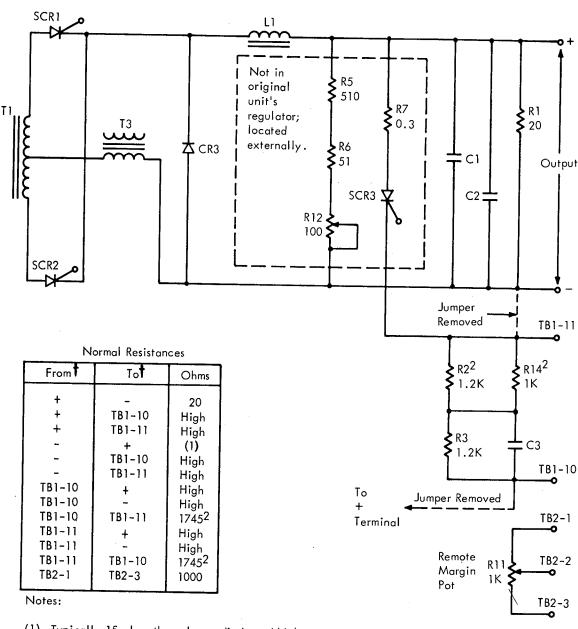

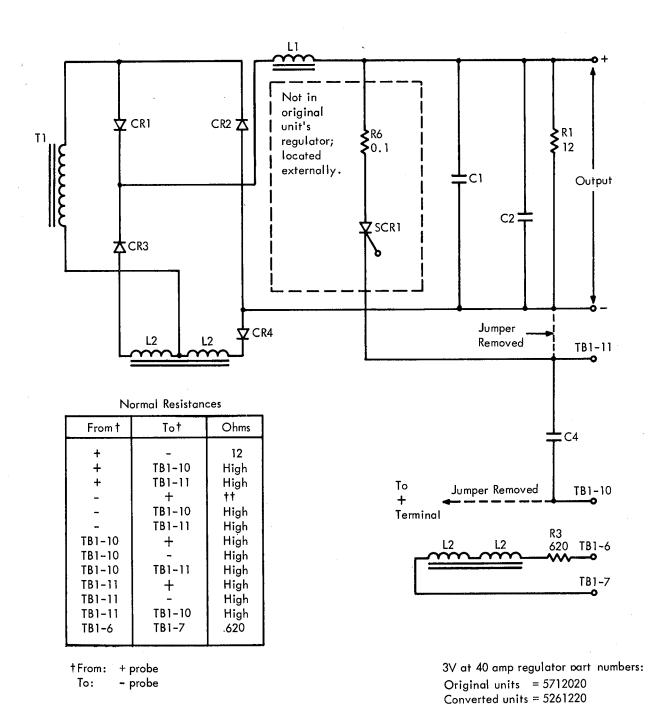

| 1-6  | Main Storage Integral Boundaries 1-7                  | 5-3        | SCR Gate Signals (Converter/Inverter) 5-7      |

|      | 2065 Circuit Levels                                   | 5-4        | Converter/Inverter                             |

| 1-7  |                                                       | 5-5        | SCR Regulator Resistances 5-9                  |

| 2-1  | Scan-In Program, Example 1                            | 5-6        | Magnetic-Amplifier Regulator Resistances       |

| 2-2  | Scan-In Program, Example 2                            | 3-6        | (4 Parts)                                      |

| 2-3  | Diagnostic Program System Master Tape Format . 2-18   | <i>c</i> 1 | Overall CPU and Main Storage Layout, Models    |

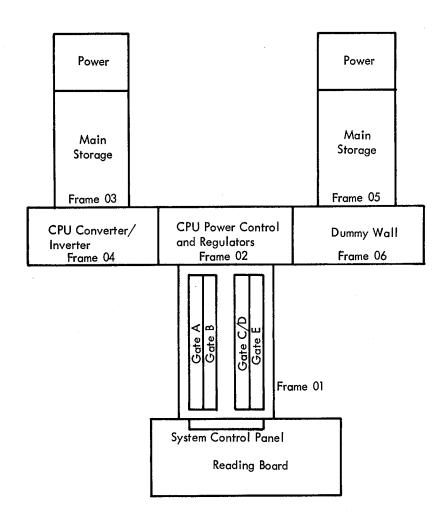

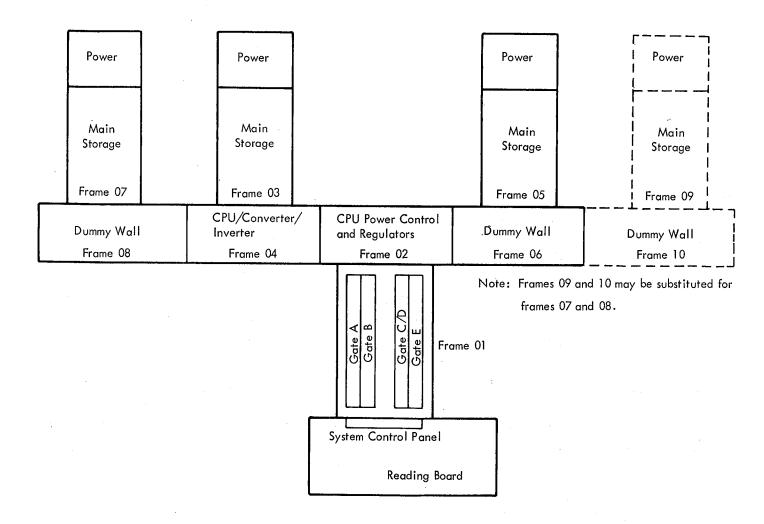

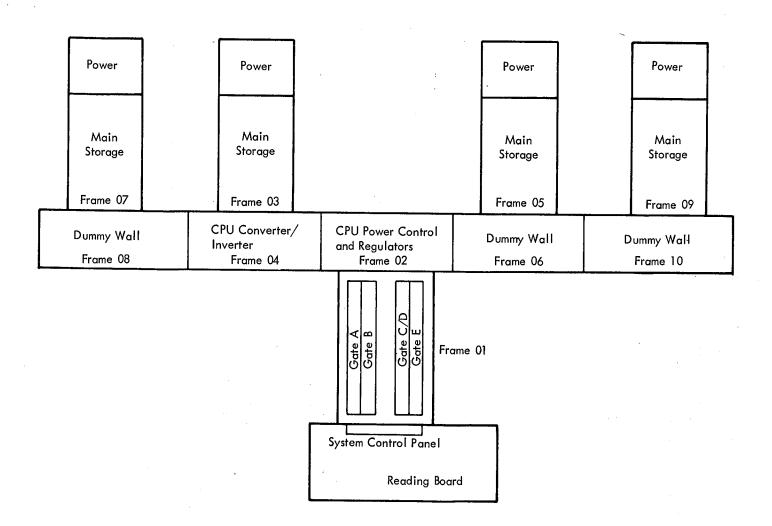

| 4-1  | Test Number Comparison Circuit 4-4                    | 6-1        |                                                |

| 4-2  | ROS Signals                                           |            | G65 and H65 6-1                                |

| 4-3  | Sense Amplifier Input Resistances 4-8                 | 6-2        | Overall CPU and Main Storage Layout,           |

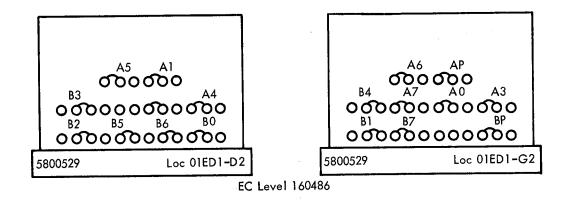

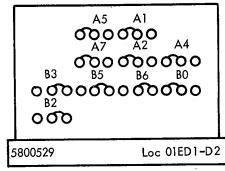

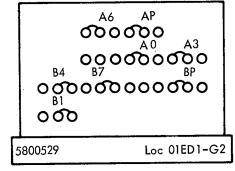

| 4-4  | ROS E1 Board                                          |            | Model I65 6-1                                  |

| 4-5  | Overall ROS Layout 4-11                               | 6-3        | Overall CPU and Main Storage Layout,           |

| 4-6  | Sync Points for FLT Zero-Cycle Troubleshooting . 4-14 |            | Model IH65 6-2                                 |

| 4-7  | FLT Timing 4-14                                       | 6-4        | Overall CPU and Main Storage Layout,           |

| 4-8  | SCOPEX Timing 4-17                                    |            | Model J65 6-2                                  |

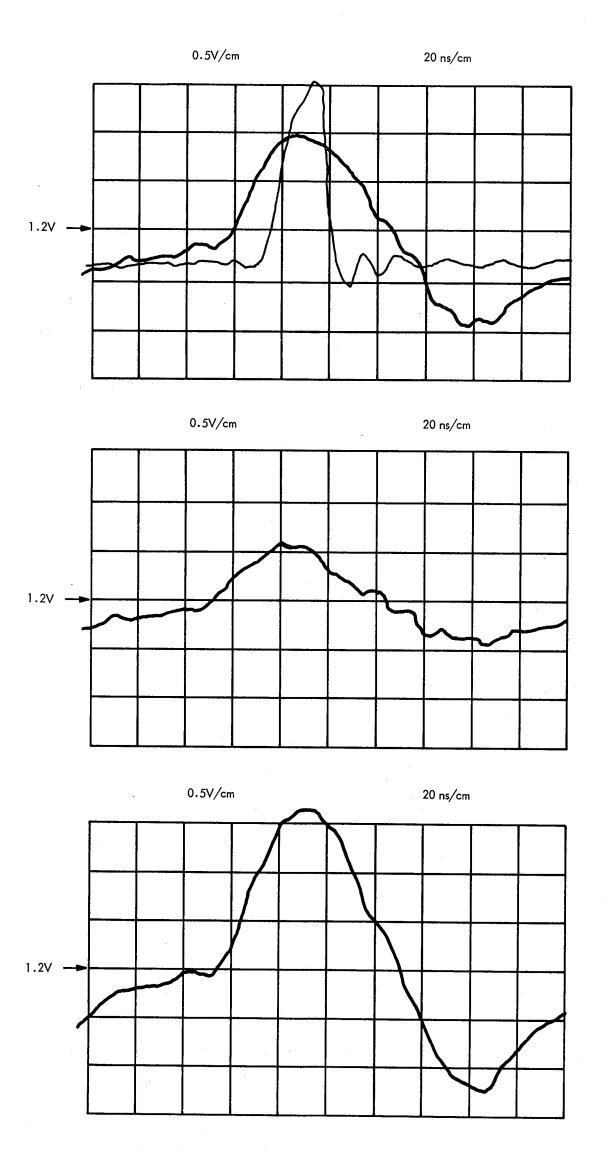

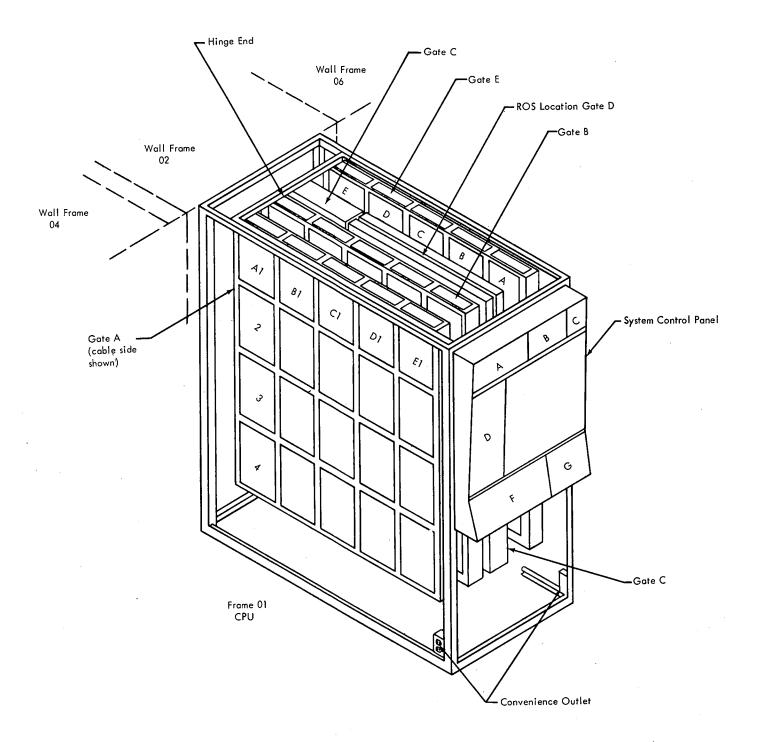

| 4-9  | ROS Sense Amplifier 1 and 0 Bit Waveforms 4-18        | 6-5        | CPU Gate and Board Locations 6-3               |

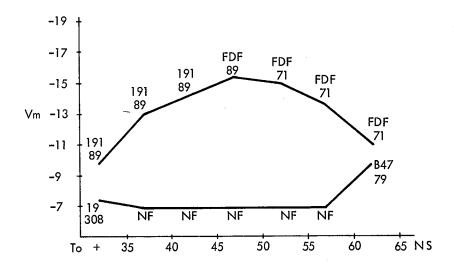

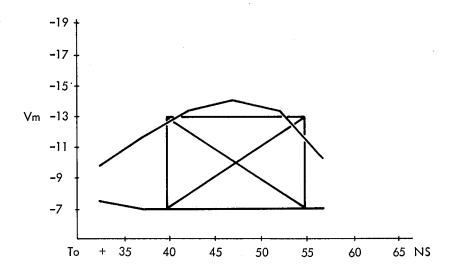

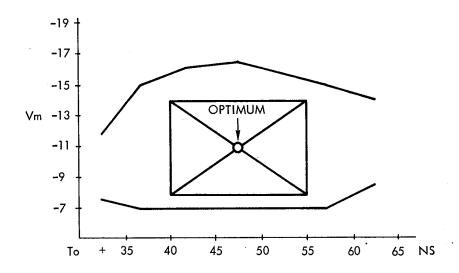

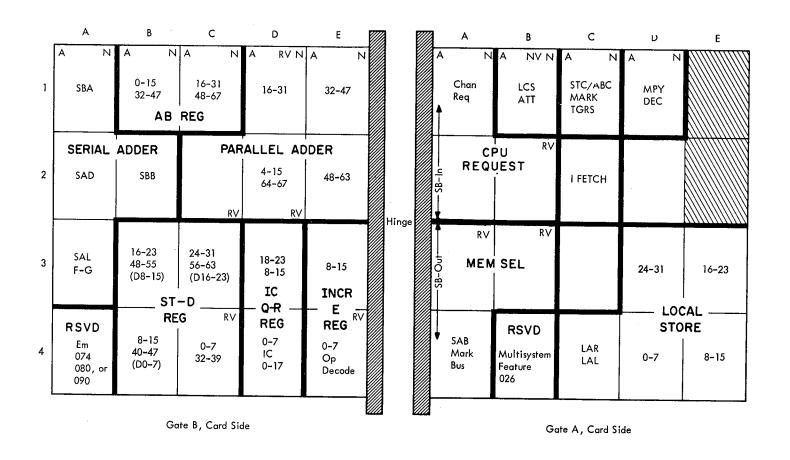

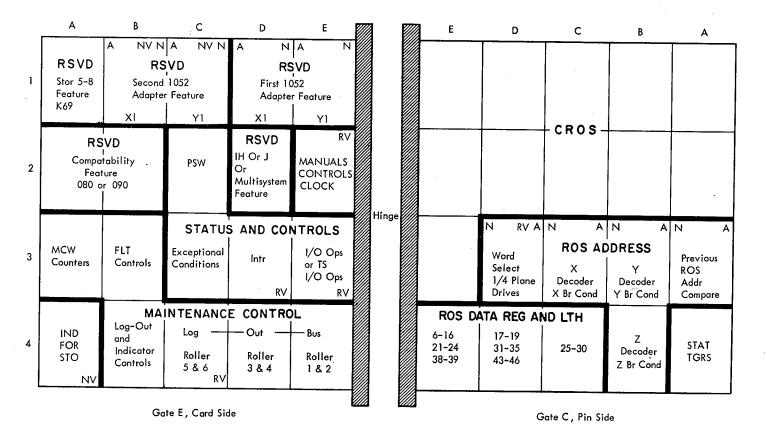

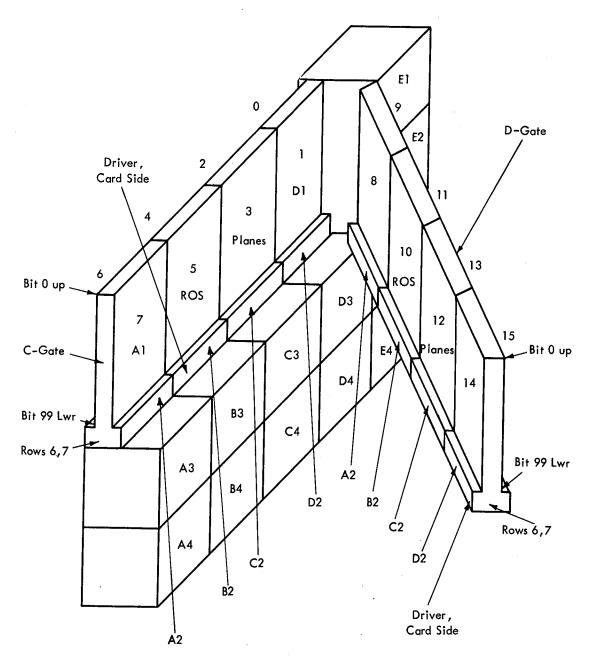

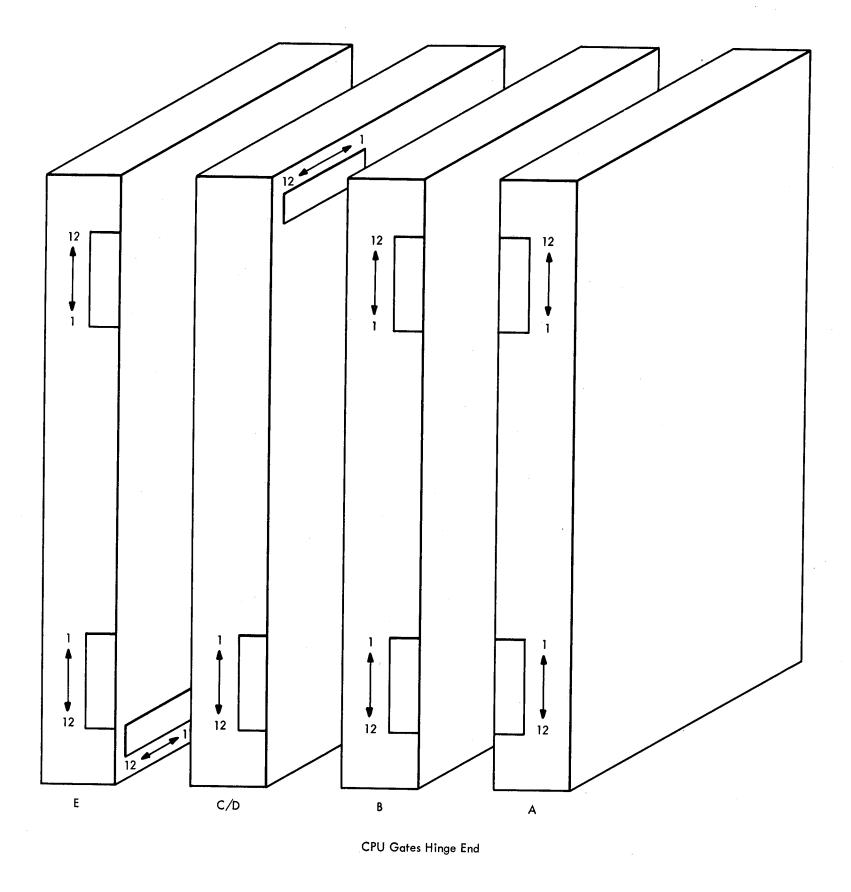

| 4-10 | Typical Shmoo 4-19                                    | 6-6        | Large Board Assignment (Functional) 6-4        |

| 4-11 | Unacceptable Shmoo 4-19                               | 6-7        | ROS Physical Layout 6-5                        |

| 4-12 | Acceptable Shmoo 4-19                                 | 6-8        | CPU Power Layout 6-6                           |

| 4-13 | ROS Sense Amplifier, Average/Weak/Strong              | 6-9        | Laminar Bus Terminal Board Locations (CPU) 6-7 |

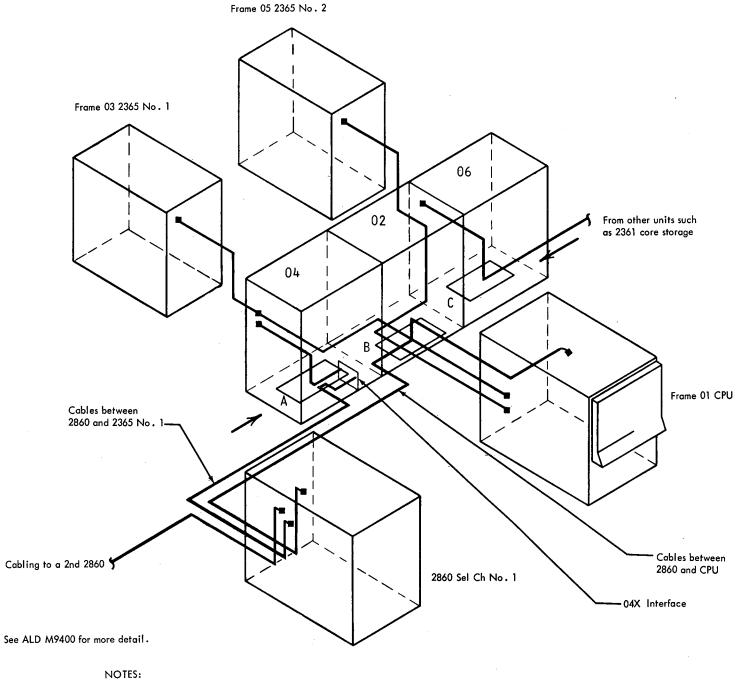

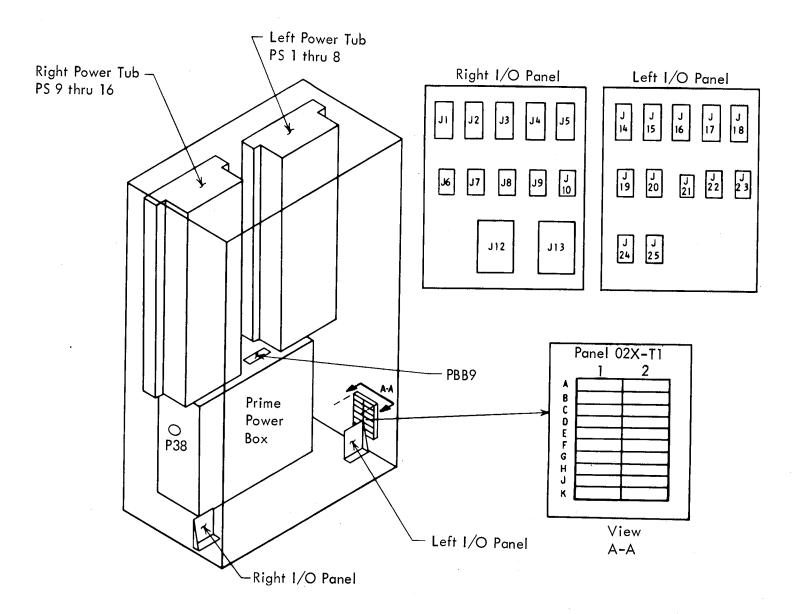

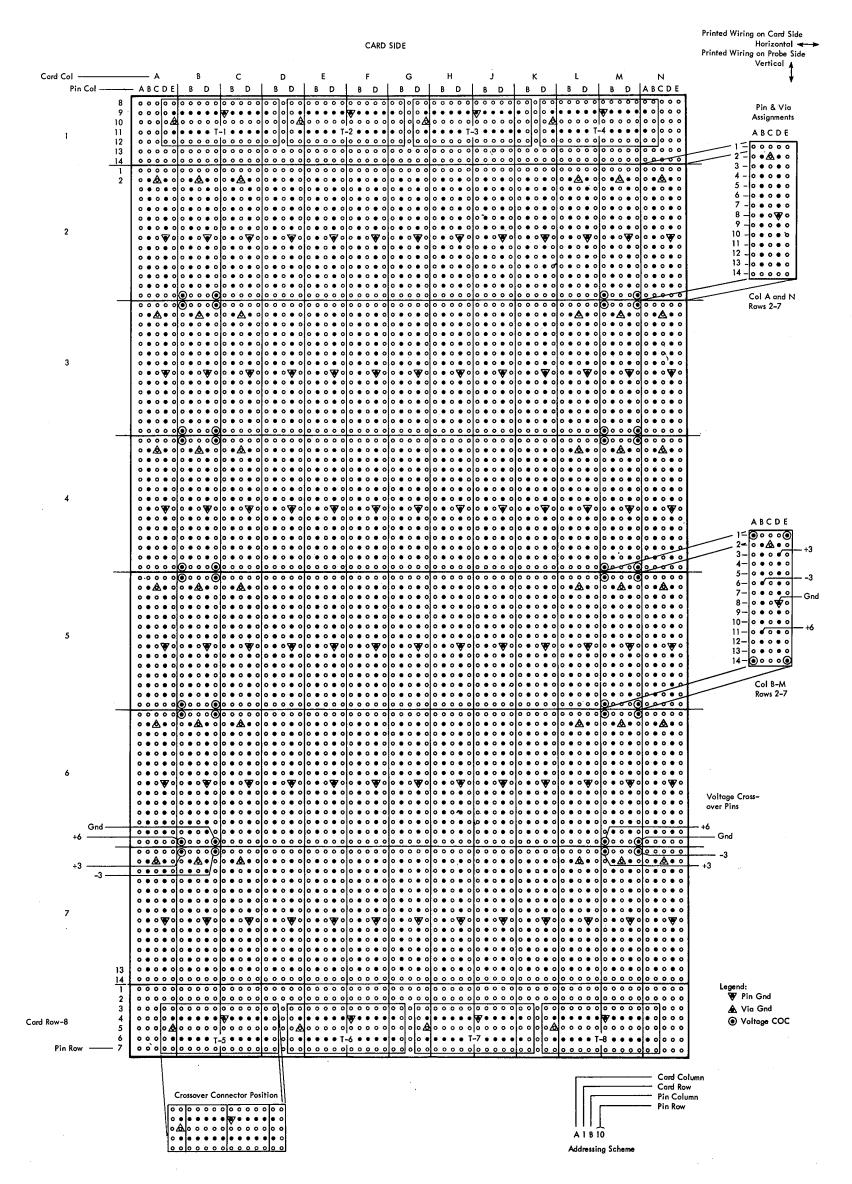

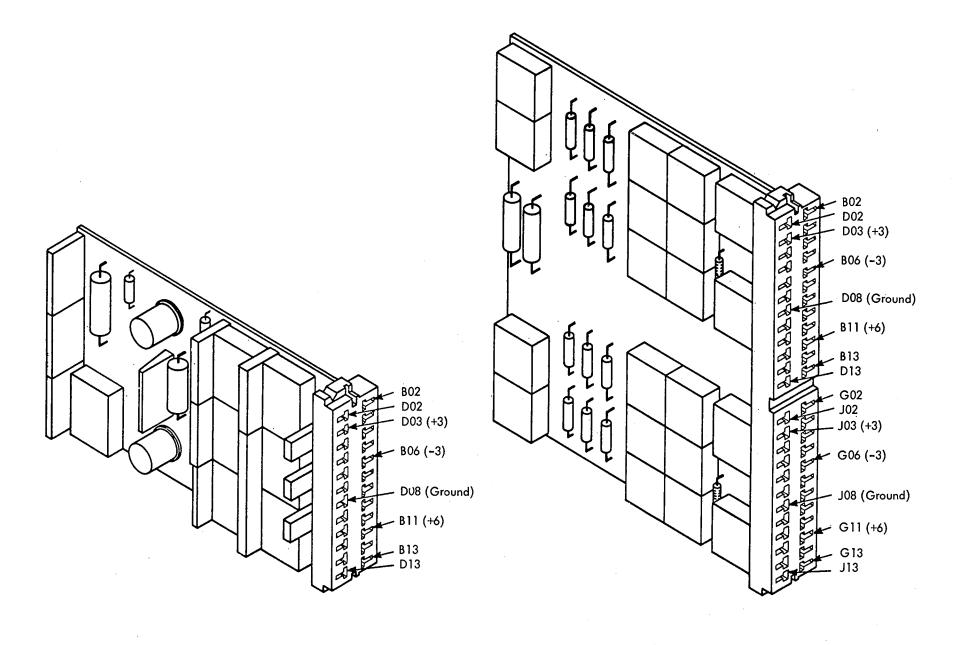

| 110  | Waveshapes                                            | 6-10       | Example of External Cable Routing 6-8          |

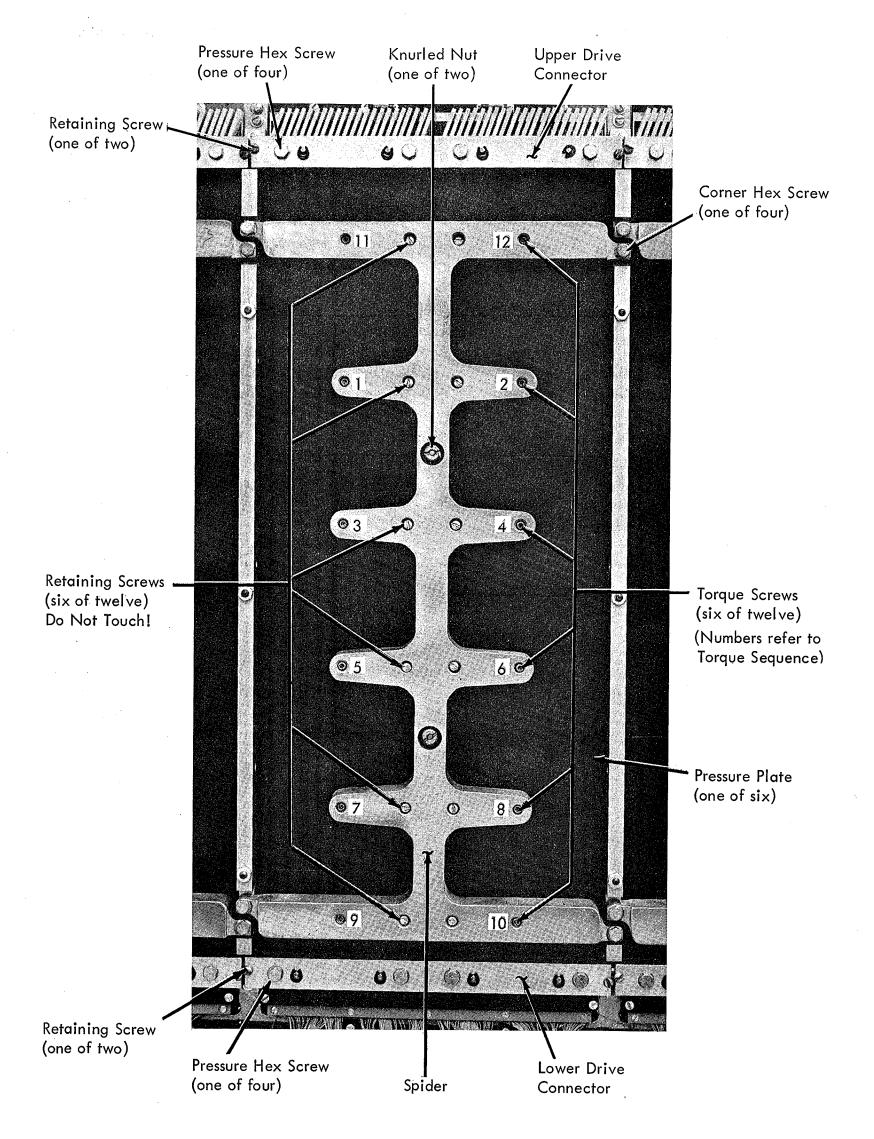

| 4-14 | ROS Pressure Spider and Torque Sequence 4-23          | 6-11       | Frame 02 Component Locations 6-9               |

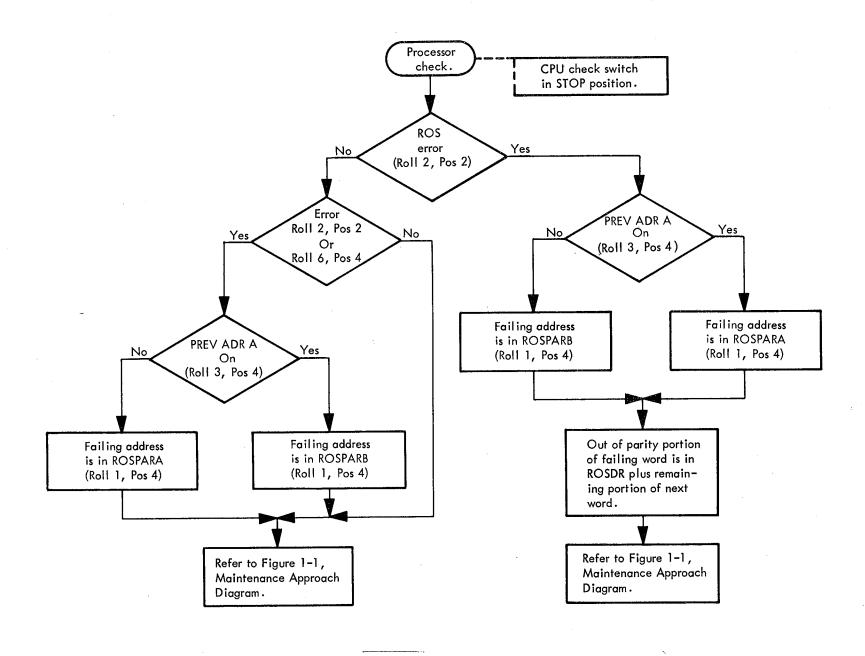

| 4-15 | Processor Checks; Determination of Failing            | 6-12       | Large Board Pin Addresses 6-10                 |

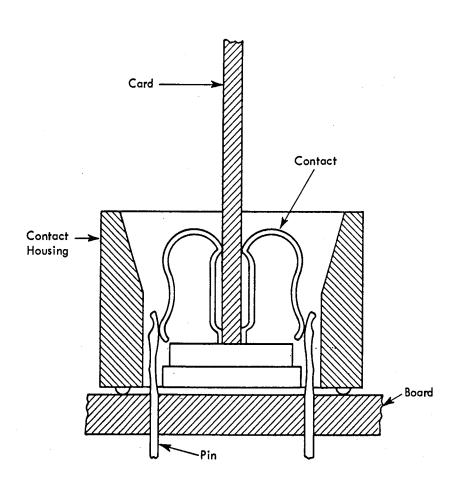

| 4-13 | ROS Cycle                                             | 6-13       | Card Contact, Board-Pin Relationship 6-11      |

| 112  |                                                       | 6-14       | Address Card Layout for 1052 Adapter 6-12      |

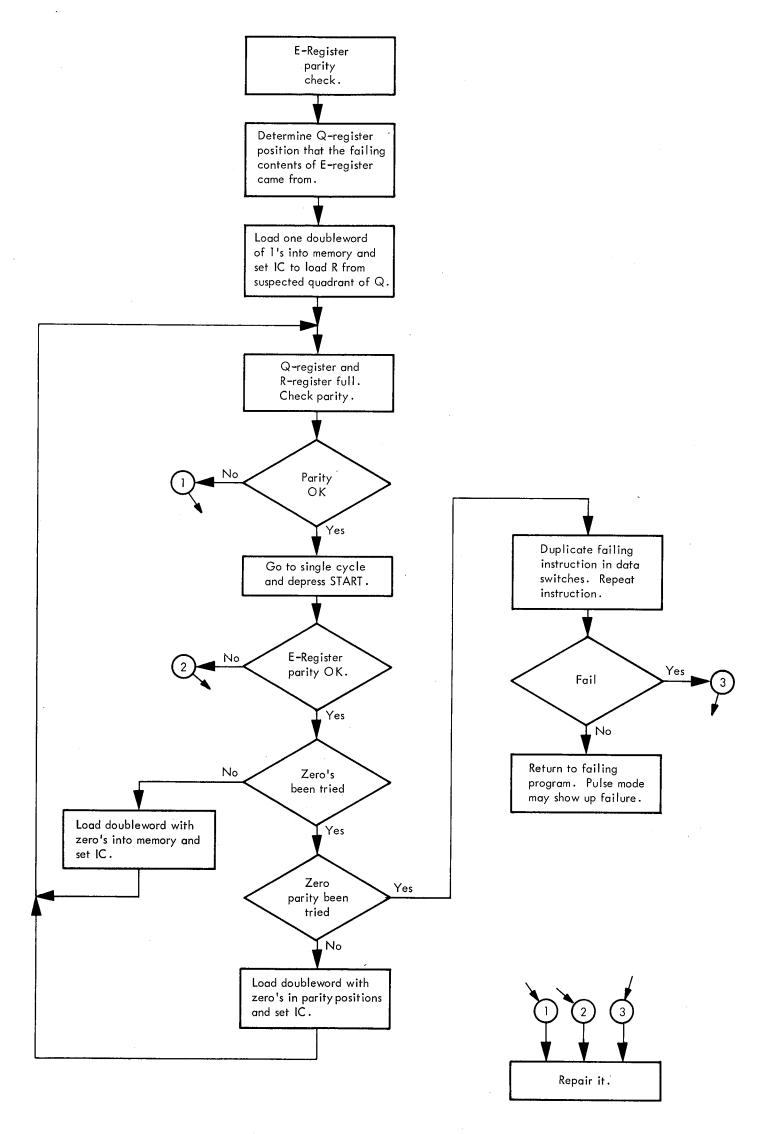

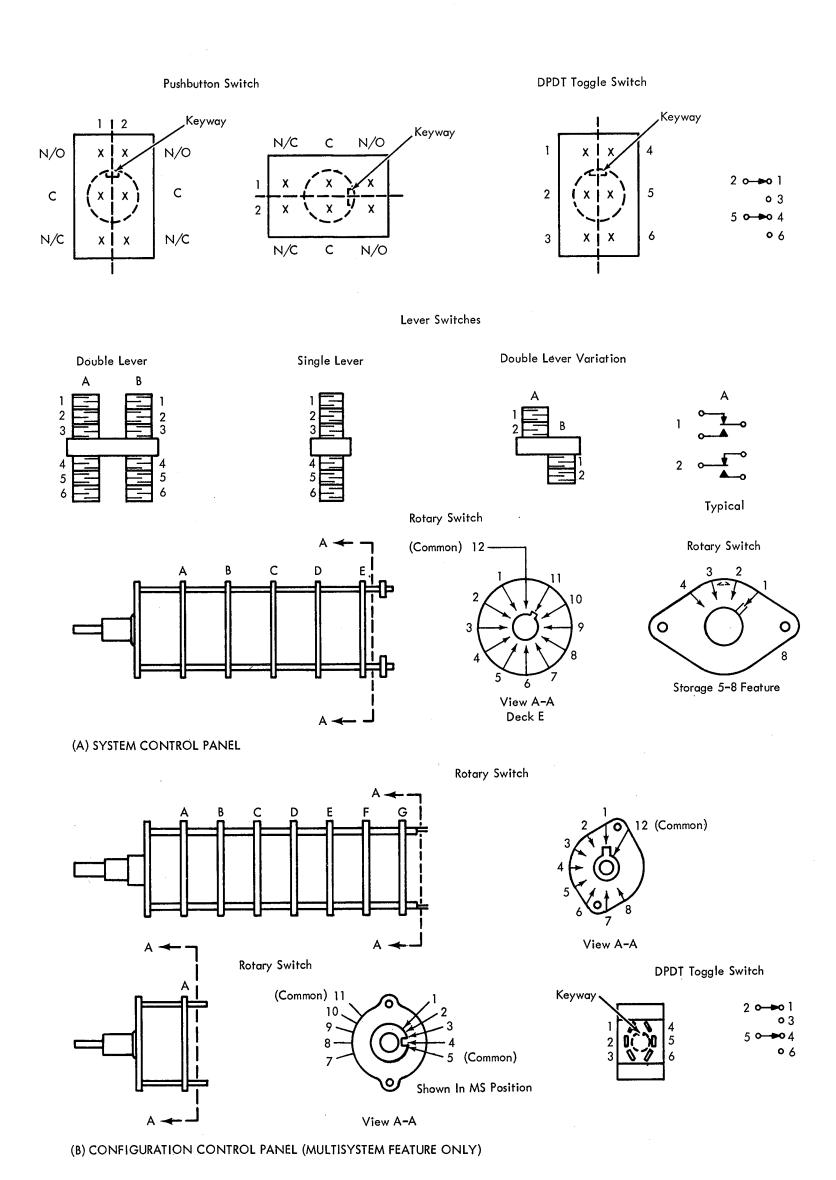

| 4-16 | E-Register Parity Check Troubleshooting 4-27          | 6-15       | Switch Contacts (Wiring Side) 6-13             |

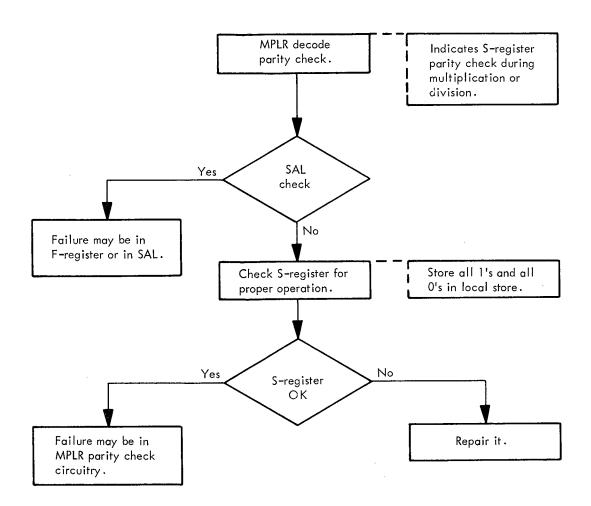

| 4-17 | MPLR Decode Parity Check Troubleshooting 4-28         |            | System Control Panel Voltmeter Calibration     |

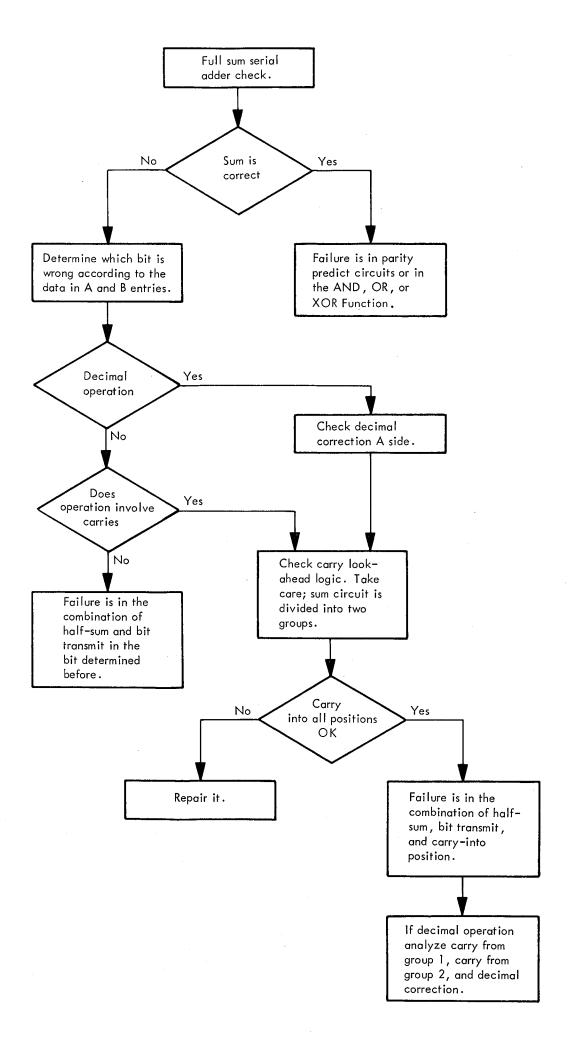

| 4-18 | Serial Adder Full-Sum Check Troubleshooting 4-29      | B-1        | · · · · · · · · · · · · · · · · · · ·          |

|      |                                                       |            | Chart                                          |

|      |                                                       |            |                                                |

|      |                                                       |            |                                                |

|      |                                                       |            |                                                |

|      |                                                       |            |                                                |

|      |                                                       |            |                                                |

|      |                                                       |            | Tables                                         |

|      |                                                       |            | 1 4.6.00                                       |

|      |                                                       |            |                                                |

|      |                                                       |            |                                                |

|      |                                                       |            | 1.04                                           |

| 1-1  | Fixed-Point Instructions                              | 1-8        | Interruptions                                  |

| 1-2  | Floating-Point Instructions 1-12                      | 1-9        | Permanent Main Storage Assignments 1-25        |

| 1-3  | Decimal Instructions 1-16                             | 2-1        | Logout Format 2-16                             |

| 1-4  | Logical Instructions 1-18                             | 2-2        | Typical Set of Diagnostic Programs for         |

| 1-5  | I/O Instructions                                      |            | System/360 Model 65 2-19                       |

| 1-6  | Branching Instructions 1-21                           | 3-1        | Preventive Maintenance Schedule 3-1            |

| 1-7  | Status Switching Instructions 1-22                    | 5-1        | DC Distribution 5-3                            |

| •    | — ······ — ··· — · · · · · · · · · · ·                |            |                                                |

# Abbreviations

| ABC          | AB register byte counter                        | hex        | hexadecimal                                     |

|--------------|-------------------------------------------------|------------|-------------------------------------------------|

| ac           | alternating current                             | HSS        |                                                 |

| ACC          | additive card code                              | Hz         | high-speed storage                              |

| adr          | address, addressed, addressing                  | п          | Hertz                                           |

| ALD          | automated logic diagram                         | IC         | in stancetical country                          |

| amp          | ampere                                          | I-Fetch    | instruction counter                             |

| ASC          | address store compare                           |            | instruction fetching                            |

| ATN          | alternate test number                           | ILC        | instruction length code                         |

| AIN          | arternate test number                           | INTRM      | intermittent                                    |

| BCD          | binary-coded decimal                            | I/O        | input/output                                    |

| BCU          | bus control unit                                | IPL        | initial program load                            |

| DCC          | ous control unit                                | T/         | 1_21_                                           |

| С            | capacitor                                       | K          | kilo                                            |

| CAS          | <del>-</del>                                    | K          | relay                                           |

| CAS          | control automation system channel address word  | kHz        | kilohertz                                       |

| CAW          | circuit breaker                                 | T A T      |                                                 |

| CC           | condition code                                  | LAL        | local storage address latches                   |

| CCC          |                                                 | LAR        | local storage address register                  |

| CCW          | channel control check<br>channel command word   | LCS        | large capacity storage                          |

| CE W         |                                                 | LS         | local storage                                   |

| CEDA         | customer engineer                               | LSWR       | local storage working register                  |

| charistic    | CPU error detection and analysis characteristic | 3640       | •                                               |

| C/I          |                                                 | MAR        | memory address register                         |

| CLD          | converter/inverter                              | max        | maximum                                         |

| CPU          | control automation system logic diagram         | MCW        | maintenance control word                        |

| CPU<br>CR    | Central Processing Unit diode                   | mHz        | megahertz                                       |

| CROS         |                                                 | MMSC       | maintenance mode stop clock                     |

| CSW          | capacitive read-only storage                    | MP         | multiprocessor                                  |

|              | channel status word                             | MPAS       | multiprocessor additional storage (5-8) feature |

| CT           | conditional terminate                           | ms         | millisecond                                     |

| <b>.</b>     | 1                                               | multisys   | multisystem                                     |

| de           | direct current                                  | •          |                                                 |

| dec div      | decimal divide                                  | no op      | no operation                                    |

| dec ovflo    | decimal overflow                                | ns         | nanosecond                                      |

| DM           | diagnostic monitor                              |            |                                                 |

| DSBL         | disable                                         | oc         | overcurrent                                     |

| DX           | first byte in a series of destination bytes     | op code    | operation code                                  |

| DX + 1       | second byte in a series of destination bytes    | oper       | operation                                       |

| DX + 2       | third byte in a series of destination bytes     | opr        | operand                                         |

| 1            |                                                 | ov         | overvoltage                                     |

| end op       | end operation                                   | _          |                                                 |

| EPO          | emergency power off                             | P          | parity                                          |

| ERSLT        | expected result                                 | PAA        | parallel adder A-side                           |

| exp ovflo    | exponent overflow                               | PAB        | parallel adder B-side                           |

| exp unflo    | exponent underflow                              | PAL        | parallel adder latch                            |

| -            | •                                               | pf         | picofarad                                       |

| F            | fuse                                            | PK         | power contactor                                 |

| FEMDM        | Field Engineering Maintenance Diagrams Manual   | PN         | part number                                     |

| FEMM         | Field Engineering Maintenance Manual            | PP         | partial product                                 |

| FETOM        | Field Engineering Theory of Operation Manual    | PQ         | partial quotient                                |

| fix-pt div   | fixed-point divide                              | PREV ADR A | previous address in ROSPARA                     |

| fix-pt ovflo | fixed-point overflow                            | priv oper  | privileged operation                            |

| FLT          | fault locating test                             | prot       | protection                                      |

| flt-pt div   | floating-point divide                           | PS         | power supply                                    |

| FLUT         | Fault Locating Utility program                  | PSW        | program status word                             |

| FPR          | floating-point register                         | R          |                                                 |

| fract        | fraction                                        |            | resistor                                        |

|              |                                                 | ROS        | read-only storage                               |

|              |                                                 | ROSAR      | read-only storage address register              |

| GCT          | gate control trigger                            | ROSBR      | read-only storage backup register               |

| G/F          | good/fail                                       | ROSDR      | read-only storage data register                 |

| GIS          | general initialization sequence                 | ROSPARA    | read-only storage previous address register A   |

| GPR          | general-purpose register                        | ROSPARB    | read-only storage previous address register B   |

|              |                                                 | RPQ        | request for price quotation                     |

| -: (10/00)   |                                                 |            |                                                 |

| SAA      | serial adder A-side                  | SW BD        | switch board                   |

|----------|--------------------------------------|--------------|--------------------------------|

| SAB      | serial adder B-side                  | sync         | synchronizing                  |

| SAB      | storage address bus                  | •            |                                |

| SAL      | serial adder latch                   | $\mathbf{T}$ | transformer                    |

| SAP      | storage address protect              | TB           | terminal board                 |

| SAR      | storage address register             | T(DX)        | table byte specified by DX     |

| SBA      | serial adder bus A                   | T(DX + 1)    | table byte specified by DX + 1 |

| SBB      | serial adder bus B                   | TIC          | transfer in channel            |

| SBBD     | select bus base drive                | TN           | test number                    |

| SBED     | select bus emitter drive             | 4            |                                |

| SCOPEX   | scoping index                        | UDC          | unit data check                |

| SCR      | silicon-controlled rectifier         | uf           | microfarad                     |

| SDBI     | storage data bus in                  | usec         | microsecond                    |

| SDBO     | storage data bus out                 | UT           | unconditional terminate        |

| signif   | significance                         |              |                                |

| SILI     | suppress incorrect length indication | V            | volt                           |

| SIP      | Systems Integration Program          | VFL          | variable-field length          |

| SLT      | solid logic technology               |              |                                |

| SMS      | standard modular system              | ≥            | greater than or equal to       |

| SOROS    | scan out read-only storage           | ≥            | greater than or equal to       |

| spec     | specification                        | <u> </u>     | less than or equal to          |

| SRL      | Systems Reference Library            | \!\!\!\!\!\! | less than or equal to          |

| STAT     | status trigger                       | =            | equal to                       |

| STC      | ST register byte counter             | <b>≠</b>     | not equal to                   |

| stg      | storage                              | &            | and                            |

| STOR CHK | storage check                        |              |                                |

|          |                                      |              |                                |

# Safety

Safety cannot be overemphasized. Always be familiar with and heed all safety precautions. Know the procedures for artificial respiration. These precautions and procedures are outlined on IBM Form 229-1264-1.

Before making any hardware changes, resistance measurements, or replacements, be sure all power is off and all capacitors are fully discharged; do not rely on bleeder resistors. Never work alone. If in doubt: Don't!

The following safety points are repeated for emphasis:

# DANGER

The internal circuitry of the converter/inverter is not isolated from the power source; therefore, a lethal potential to ground is present whenever power is on.

Exercise extreme caution. This potential exists on the SMS cards, heat sinks, and terminals to the regulators.

# **DANGER**

The converter/inverter assembly weighs approximately 150 pounds. To avoid personal injury, three men are required to remove and replace it. The area must be clear to permit easy and safe manipulation of the assembly.

# **DANGER**

The input terminals of the regulators are not isolated from the power source; therefore, a lethal potential to ground is present whenever power is on. Exercise extreme caution. This chapter contains reference information needed for servicing the System/360 Model 65. Information is in tabular form where possible. Diagrams are largely reserved for the FEMDM but are cross-referenced here when appropriate.

# 1.1 DATA FLOW AND CONTROL

Data flow diagrams are found in the 2065 Processing Unit FEMDM, Form Y27-2038. These diagrams fall into the following categories:

System data flow

CPU data flow

Diagram 3-1

Diagram 3-2

Data flow by instruction class

Scan data flow and control

Diagram 8-101

Data flow is discussed in Chapter 1, Section 1, of the 2065 Processing Unit FETOM, Form Y27-2036.

# 1.2 SYSTEM CODING

The codes and formats used for instructions and data within the Model 65 are described in the subparagraphs that follow.

# 1.2.1 Hexadecimal/Decimal Conversion

Powers of 2 and 16 are listed in Figure 1-1. The charts and procedures for converting binary, hexadecimal, and decimal numbers and fractions are shown in Figure 1-2.

|   | 2 <sup>n</sup>                                                     | l n                  | 2 <sup>-n</sup>                                                                                                                                                                                      | 16 <sup>n</sup>                                                                                           | n                                    |

|---|--------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------|

|   | 1<br>2<br>4<br>8                                                   | 0<br>1<br>2<br>3     | 1.0<br>0.5<br>0.25<br>0.125                                                                                                                                                                          | 1<br>16<br>256<br>4 096                                                                                   | 2 3                                  |

|   | 16<br>32<br>64<br>128                                              | 4<br>5<br>6<br>7     | 0.062 5<br>0.031 25<br>0.015 625<br>0.007 812 5                                                                                                                                                      | 65 536<br>1 048 576<br>16 777 216<br>268 435 456<br>4 294 967 296                                         | 5<br>6<br>7<br>8                     |

| • | 256<br>512<br>1 024<br>2 048                                       | 8<br>9<br>10<br>11   | 0.003 906 25<br>0.001 953 125<br>0.000 976 562 5<br>0.000 488 281 25                                                                                                                                 | 68 719 476 736<br>1 099 511 627 776<br>17 592 186 044 416<br>281 474 976 710 656<br>4 503 599 627 370 496 | 10 = A<br>11 = B<br>12 = C<br>13 = D |

|   | 4 096<br>8 192<br>16 384<br>32 768                                 | 12<br>13<br>14<br>15 | 0.000 244 140 625<br>0.000 122 070 312 5<br>0.000 061 035 156 25<br>0.000 030 517 578 125                                                                                                            | 72 057 594 037 927 936<br>1 152 921 504 606 846 976<br>Decimal Values                                     |                                      |

|   | 65 536<br>131 072<br>262 144<br>524 288                            | 16<br>17<br>18<br>19 | 0.000 015 258 789 062 5<br>0.000 007 629 394 531 25<br>0.000 003 814 697 265 625<br>0.000 001 907 348 632 812 5                                                                                      |                                                                                                           |                                      |

|   | 1 048 576<br>2 097 152<br>4 194 304<br>8 388 608                   | 20<br>21<br>22<br>23 | 0.000 000 953 674 316 406 25<br>0.000 000 476 837 158 203 125<br>0.000 000 238 418 579 101 562 5<br>0.000 000 119 209 289 550 781 25                                                                 |                                                                                                           |                                      |

|   | 16 777 216<br>33 554 432<br>67 108 864<br>134 217 728              | 24<br>25<br>26<br>27 | 0.000 000 059 604 644 775 390 625<br>0.000 000 029 802 322 387 695 312 5<br>0.000 000 014 901 161 193 847 656 25<br>0.000 000 007 450 580 596 923 828 125                                            |                                                                                                           |                                      |

|   | 268 435 456<br>536 870 912<br>1 073 741 824<br>2 147 483 648       | 28<br>29<br>30<br>31 | 0.000 000 003 725 290 298 461 914 062 5<br>0.000 000 001 862 645 149 230 957 031 25<br>0.000 000 000 931 322 574 615 478 515 625<br>0.000 000 000 465 661 287 307 739 257 812 5                      |                                                                                                           |                                      |

|   | 4 294 967 296<br>8 589 934 592<br>17 179 869 184<br>34 359 738 368 | 32<br>33<br>34<br>35 | 0.000 000 000 232 830 643 653 869 628 906 25<br>0.000 000 000 116 415 321 826 934 814 453 125<br>0.000 000 000 058 207 660 913 467 407 226 562 5<br>0.000 000 000 029 103 830 456 733 703 613 281 25 |                                                                                                           |                                      |

Figure 1-1. Powers of 2 and 16

Hexadecimal and Decimal Integer Conversion Table

|     | HALFWORD      |     |             |     |            |     |         |      |           | HALFWORD |         |     |         |     |         |

|-----|---------------|-----|-------------|-----|------------|-----|---------|------|-----------|----------|---------|-----|---------|-----|---------|

|     | BYTE BYTE     |     |             |     |            |     |         |      | BYTE BYTE |          |         |     |         |     |         |

|     | 01 23         |     | 4567        |     | 0123       |     | 567     | · 01 | 23        | 45       | 567     | 0   | 23 4567 |     |         |

| Hex | Decimal       | Hex | Decimal     | Hex | Decimal    | Hex | Decimal | Hex  | Decimal   | Hex      | Decimal | Hex | Decimal | Hex | Decimal |

| 0   | 0             | 0 . | 0           | 0   | 0          | 0   | 0       | 0    | 0         | 0 .      | 0       | 0   | 0       | 0   | 0       |

| 1   | 268,435,456   | 1   | 16,777,216  | 1   | 1,048,576  | 1   | 65,536  | ı    | 4,096     | 1        | 256     | 1   | 16      | 1   | 1       |

| 2   | 536,870,912   | 2   | 33,554,432  | 2   | 2,097,152  | 2   | 131,072 | 2    | 8,192     | 2        | 512     | 2   | 32      | 2   | 2       |

| 3   | 805,306,368   | 3   | 50,331,648  | 3   | 3,145,728  | 3   | 196,608 | 3    | 12,288    | 3        | 768     | 3   | 48      | 3   | 3       |

| 4   | 1,073,741,824 | 4   | 67,108,864  | .4  | 4,194,304  | 4   | 262,144 | 4    | 16,384    | 4        | 1,024   | 4   | 64      | 4   | 4       |

| 5   | 1,342,177,280 | 5   | 83,886,080  | 5   | 5,242,880  | 5   | 327,680 | 5    | 20,480    | 5        | 1,280   | 5   | 80      | 5   | 5       |

| 6   | 1,610,612,736 | 6   | 100,663,296 | 6   | 6,291,456  | 6   | 393,216 | 6    | 24,576    | 6        | 1,536   | 6   | 96      | 6   | 6       |

| 7   | 1,879,048,192 | 7   | 117,440,512 | 7   | 7,340,032  | 7   | 458,752 | 7    | 28,672    | 7        | 1,792   | 7   | 112     | 7   | 7       |

| 8   | 2,147,483,648 | 8   | 134,217,728 | 8   | 8,388,608  | 8   | 524,288 | 8    | 32,768    | 8        | 2,048   | 8   | 128     | 8   | 8       |

| 9   | 2,415,919,104 | 9   | 150,994,944 | 9   | 9,437,184  | 9   | 589,824 | 9    | 36,864    | 9        | 2,304   | 9   | 144     | 9   | 9       |

| Α   | 2,684,354,560 | Α   | 167,772,160 | Α   | 10,485,760 | Α   | 655,360 | Α    | 40,960    | Α        | 2,560   | Α   | 160     | Α   | 10      |

| В   | 2,952,790,016 | В   | 184,549,376 | В   | 11,534,336 | В   | 720,896 | В    | 45,056    | В        | 2,816   | В   | 176     | В   | 11      |

| С   | 3,221,225,472 | С   | 201,326,592 | С   | 12,582,912 | С   | 786,432 | С    | 49,152    | С        | 3,072   | С   | 192     | С   | 12      |

| D   | 3,489,660,928 | D   | 218,103,808 | D   | 13,631,488 | D   | 851,968 | D    | 53,248    | D        | 3,328   | D   | 208     | D   | 13      |

| E   | 3,758,096,384 | E   | 234,881,024 | E   | 14,680,064 | Е   | 917,504 | E    | 57,344    | E        | 3,584   | E   | 224     | Ε   | 14      |

| F   | 4,026,531,840 | F   | 251,658,240 | F   | 15,728,640 | F   | 983,040 | F    | 61,440    | F        | 3,840   | F   | 240     | F   | 15      |

|     | 8             |     | 7           |     | 6          |     | 5       |      | 4         |          | 3       | l   | 2       |     | 1       |

Hexadecimal and Decimal Fraction Conversion Table,

|     | HALFWORD |      |               |      |      |       |               |      |       |       |         |         |      |

|-----|----------|------|---------------|------|------|-------|---------------|------|-------|-------|---------|---------|------|

|     |          | BYTE |               |      |      | ВҮТЕ  |               |      |       |       |         |         |      |

|     | 0123     |      | 456           | 7    |      |       | 0123          |      |       |       | 4567    | 7       |      |

| Hex | Decimal  | Hex  | Deci          | mal  | Hex  | - 1   | Decima        | 1    | Hex   | Dec   | cimal E | quivale | nt   |

| .0  | .0000    | .00  | .0000         | 0000 | .000 | .0000 | 0000          | 0000 | .0000 | .0000 | 0000    | 0000    | 0000 |

| .1  | .0625    | .01  | .0039         | 0625 | .001 | .0002 | 4414          | 0625 | .0001 | .0000 | 1525    | 8789    | 0625 |

| . 2 | .1250    | .02  | .0078         | 1250 | .002 | .0004 | 8828          | 1250 | .0002 | .0000 | 3051    | 7578    | 1250 |

| .3  | .1875    | .03  | .011 <i>7</i> | 1875 | .003 | .0007 | 3242          | 1875 | .0003 | .0000 | 4577    | 6367    | 1875 |

| . 4 | .2500    | .04  | .0156         | 2500 | .004 | .0009 | 7656          | 2500 | .0004 | .0000 | 6103    | 5156    | 2500 |

| .5  | .3125    | . 05 | .0195         | 3125 | .005 | .0012 | 2070          | 3125 | .0005 | .0000 | 7629    | 3945    | 3125 |

| .6  | .3750    | .06  | .0234         | 3750 | .006 | .0014 | 6484          | 3750 | .0006 | .0000 | 9155    | 2734    | 3750 |

| .7  | .4375    | .07  | .0273         | 4375 | .007 | .0017 | 0898          | 4375 | .0007 | .0001 | 0681    | 1523    | 4375 |

| .8  | .5000    | .08  | .0312         | 5000 | .008 | .0019 | 531 2·        | 5000 | .0008 | .0001 | 2207    | 0312    | 5000 |

| .9  | .5625    | .09  | .0351         | 5625 | .009 | .0021 | 9726          | 5625 | .0009 | .0001 | 3732    | 9101    | 5625 |

| .А  | . 6250   | .0A  | .0390         | 6250 | .00A | .0024 | 4140          | 6250 | .000A | .0001 | 5258    | 7890    | 6250 |

| .В  | . 6875   | .OB  | .0429         | 6875 | .00B | .0026 | 8554          | 6875 | .000B | .0001 | 6784    | 6679    | 6875 |

| .c  | .7500    | .0C  | .0468         | 7500 | .00C | .0029 | 2968          | 7500 | .000C | .0001 | 8310    | 5468    | 7500 |

| .D  | .8125    | .0D  | .0507         | 8125 | .00D | .0031 | 7382          | 8125 | .000D | .0001 | 9836    | 4257    | 812  |

| .E  | .8750    | .OE  | .0546         | 8750 | .00E | .0034 | 1 <i>7</i> 96 | 8750 | .000E | .0002 | 1362    | 3046    | 8750 |

| .F  | .9375    | .OF  | .0585         | 9375 | .00F | .0036 | 6210          | 9375 | .000F | .0002 | 2888    | 1835    | 937. |

|     | 1        | 2    |               | 3    |      |       |               |      |       | 4     |         |         |      |

Example of use of fraction table. Convert hex .ABC to decimal value:

Find: .A (highest order) = .6250

.0B (next order) = .0429 6875

.00C (next order) = .0029 2968 7500

Add all ordered values: = .6708 9843 7500 (decimal equivalent)

Note: If the problem were to convert hex 1B6.ABC to decimal value, all that would be necessary has been shown above and in the first example (consider the two examples combined). The decimal equivalent is: 438.6708 9843 7500.

Figure 1-2. Binary and Hexadecimal Conversion Charts (Part 1 of 2)

#### TO CONVERT HEXADECIMAL TO DECIMAL

- Locate the column of decimal numbers corresponding to the leftmost digit or letter of the hexadecimal; select from this column and record the number that corresponds to the position of the hexadecimal digit or letter.

- 2. Repeat step 1 for the next (second from the left) position.

- 3. Repeat step 1 for the units (third from the left) position.

- 4. Add the numbers selected from the table to form the decimal number.

#### TO CONVERT DECIMAL TO HEXADECIMAL

- (a) Select from the table the highest decimal number that is equal to or less than the number to be converted.

- (b) Record the hexadecimal of the column containing the selected number.

- (c) Subtract the selected decimal from the number to be converted.

- 2. Using the remainder from step 1 (c), repeat all of step 1 to develop the second position of the hexadecimal (and a remainder).

- 3. Using the remainder from step 2, repeat all of step 1 to develop the units position of the hexadecimal.

- 4. Combine terms to form the hexadecimal number.

| EXAMPLE                            |      |  |  |  |  |  |

|------------------------------------|------|--|--|--|--|--|

| Conversion of<br>Hexadecimal Value | D34  |  |  |  |  |  |

| 1. D                               | 3328 |  |  |  |  |  |

| 2. 3                               | 48   |  |  |  |  |  |

| 3. 4                               | 4    |  |  |  |  |  |

| 4. Decimal                         | 3380 |  |  |  |  |  |

|    | convert integer numbers greater than the capacity table, use the techniques below: |

|----|------------------------------------------------------------------------------------|

| HE | XADECIMAL TO DECIMAL                                                               |

|    | ccessive cumulative multiplication from left to nt, adding units position.         |

| Example: | D34 <sub>16</sub> | = 3380 <sub>10</sub> | D = | 13<br>×16   |

|----------|-------------------|----------------------|-----|-------------|

|          |                   |                      |     | 208         |

|          |                   |                      | 3 = | + 3         |

|          |                   |                      |     | 211         |

|          |                   |                      |     | <u>x16</u>  |

|          |                   |                      |     | 3376        |

|          |                   |                      | 4 = | + 4         |

|          |                   |                      |     | <u>3380</u> |

| EXAMPLE                        |                    |

|--------------------------------|--------------------|

| Conversion of<br>Decimal Value | 3380               |

| 1. D                           | <u>-3328</u><br>52 |

| 2. 3                           | -48<br>-48         |

| 3. 4                           | 4                  |

| 4. Hexadecimal                 | D34                |

# DECIMAL TO HEXADECIMAL

Divide and collect the remainder in reverse order.

Figure 1-2. Binary and Hexadecimal Conversion Charts (Part 2 of 2)

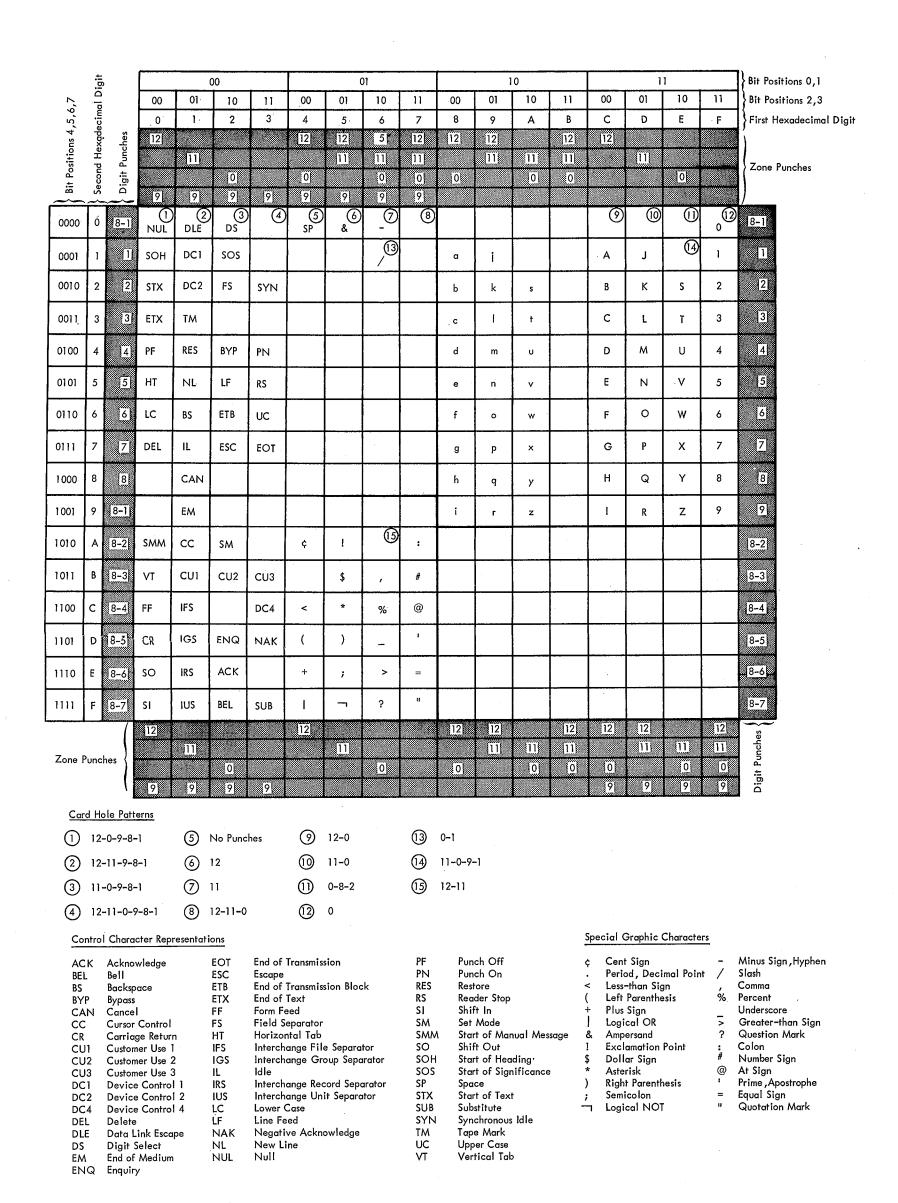

# 1.2.2 Eight-Bit Zoned Character Codes (USASCII-8 & EBCDIC)

The two standard data codes are the Extended Binary-Coded-Decimal Interchange Code (EBCDIC) and the USA Standard Code for Information Interchange extended to eight bits (USASCII-8). Both EBCDIC and USASCII-8 provide for 256 possible characters. Each character is composed of eight bits (one byte) and each bit position is assigned a number. The numbering conventions differ for each code. The conventions are:

| Bit | os  | iti   | on      |   |             |                                |

|-----|-----|-------|---------|---|-------------|--------------------------------|

| 0 1 | 2   | 3     | 4       | 5 | 6           | 7                              |

| 8 7 | 6   | 5     | 4       | 3 | 2           | 1                              |

|     | 0 1 | 0 1 2 | 0 1 2 3 |   | 0 1 2 3 4 5 | 0 1 2 3 4 5 6<br>8 7 6 5 4 3 2 |

In addition the seven-bit USASCII code can be imbedded, or recoded, into USASCII-8 as follows:

| Code      | Bit Position    |

|-----------|-----------------|

| ÜSASCII   | 76754321        |

| USASCII-8 | 8 7 6 5 4 3 2 1 |

The EBCDIC codes are shown in Figure 1-3. The USASCII-8 codes are shown in Figure 1-4.

In Figure 1-3, the 256-position chart outlined by the heavy black lines, shows the graphic characters and control character representations for EBCDIC. The bit-position numbers, bit patterns, hexadecimal representations and card hole patterns for these and other possible EBCDIC characters are also shown.

Figure 1-3. EBCDIC Code

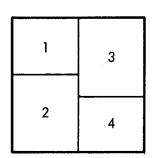

To find the card hole patterns for most characters, partition the 256-position chart into four blocks as follows:

- Block 1: Zone punches at top of chart; digit punches at left

- Block 2: Zone punches at bottom of chart; digit punches at left

- Block 3: Zone punches at top of chart; digit punches at right

- Block 4: Zone punches at bottom of chart; digit punches at right

Fifteen positions in the chart are exceptions to the above arrangement. These positions are indicated by small numbers in the upper right corners of their corresponding boxes, and the card hole patterns for these positions are given at the bottom of the chart. Bit-position numbers, bit patterns, and hexadecimal representations for these positions are found in the usual manner.

Following are some examples of the use of the EBCDIC chart:

| Character | Туре                                               | Bit Pattern | Hex | Hole            | Pattern        |

|-----------|----------------------------------------------------|-------------|-----|-----------------|----------------|

|           |                                                    |             |     | Zone Punches    | Digit Punches  |

| PF        | Control Character                                  | 00 00 0100  | 04  | 12 - 9          | - 4            |

| %         | Special Graphic                                    | 01 10 1100  | 6C  | 0               | - 8 - 4        |

| R         | Upper Case                                         | 11 01 1001  | D9  | 11              | - 9            |

| а         | Lower Case                                         | 10 00 0001  | 81  | 12 - 0          | -              |

|           | Control Character,<br>function not yet<br>assigned | 00 11 0000  | 30  | 12 - 11 - 0 - 9 | <b>-</b> 8 - 1 |

Bit Positions 01 23 4567

# 1.2.3 Instructions and Instruction Formats

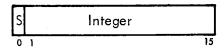

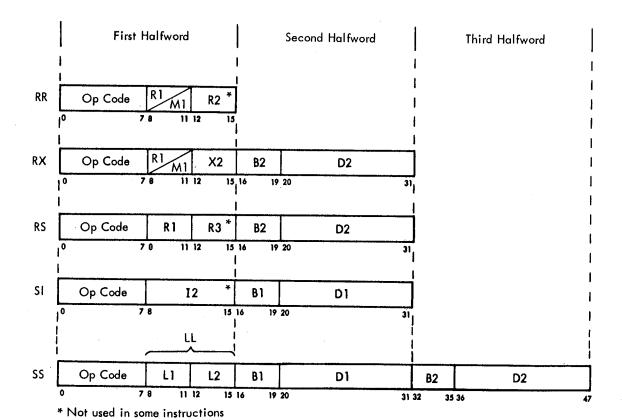

Tables 1-1 through 1-7 list the 2065 instructions according to instruction class. Model 65 instruction formats are shown in Figure 1-5.

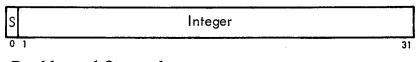

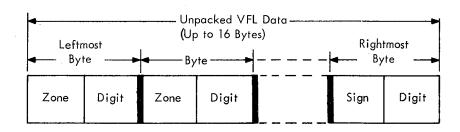

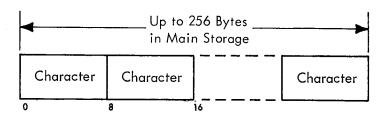

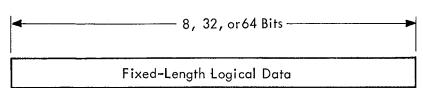

# 1.2.4 Data Formats

The data may be divided into four classifications:

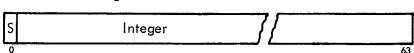

1. Fixed-point numbers, having a binary radix and a fixed length:

Halfword Operand

Word Operand

**Doubleword Operand**

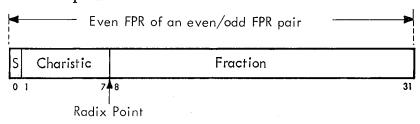

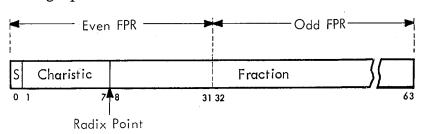

2. Floating-point numbers, represented by a seven-bit characteristic and a signed hex fraction:

# Short Operand

# Long Operand

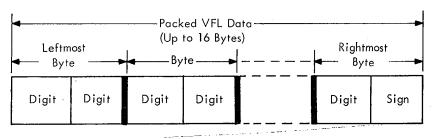

3. Decimal numbers, represented by four-bit binary-coded-decimal (BCD) digits:

# Packed:

# Unpacked (Zoned)

4. Logical information, represented by eight-bit zoned character codes:

# VFL Format:

# Fixed-Length Format

The main storage integral boundaries for data and instructions are shown in Figure 1-6.

|                       | Ω           |     |     |    |    |    |    |    |    |    |    |    |    |    |          |    |     |                         |

|-----------------------|-------------|-----|-----|----|----|----|----|----|----|----|----|----|----|----|----------|----|-----|-------------------------|

| Bit Positions 4,3,2,1 | Hexadecimal |     |     |    |    |    |    |    |    |    |    |    |    |    |          |    |     |                         |

| , 4 st                | xade        |     |     |    |    |    |    |    |    |    |    |    |    |    |          |    |     |                         |

| ÷ior                  |             |     | ţ   |    |    |    |    |    |    |    |    |    |    |    |          |    |     | D == = ==               |

| osi                   | puc         |     | 0   | 0  | ,  |    | 0  |    |    |    | ]  | 0  |    |    | 1        |    |     | Bit Positions 8,7       |

|                       | Second      | 00  | 01  | 10 | 11 | 00 | 01 | 10 | 11 | 00 | 01 | 10 | 11 | 00 | 01       | 10 | 11  | Bit Positions 6,5       |

| ~~~                   | ~~~         | 0   | 1   | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | Α  | В  | С  | D        | E  | F   | First Hexadecimal Digit |

| 0000                  | 0           | NUL | DLE |    |    | SP | 0  |    |    |    |    | @  | Р  |    |          | `  | р   |                         |

| 0001                  | 1           | SOH | DC1 |    |    | ē  | 1  |    |    |    |    | Α  | Ø  |    |          | а  | q   |                         |

| 0010                  | 2           | STX | DC2 |    |    | 11 | 2  |    |    |    |    | В  | R  |    |          | b  | r   |                         |

| 0011                  | 3           | ETX | DC3 |    |    | #  | 3  |    |    |    |    | С  | S  |    |          | С  | s   |                         |

| 0100                  | 4           | EOT | DC4 |    |    | \$ | 4  |    |    |    |    | D  | T  |    |          | d  | Ť   |                         |

| 0101                  | 5           | ENQ | NAK |    |    | %  | 5  |    |    |    |    | E  | U  |    |          | е  | U   |                         |

| 0110                  | 6           | ACK | SYN |    |    | &  | 6  |    |    |    |    | F  | ٧  |    |          | f  | ٧   |                         |

| 0111                  | 7           | BEL | ETB |    |    | 1  | 7  |    |    |    |    | G  | W  |    |          | g  | w   |                         |

| 1000                  | 8           | BS  | CAN |    |    | (  | 8  |    |    |    |    | Н  | Х  |    |          | h  | ×   | ·                       |

| 1001                  | 9           | HT  | EM  |    |    | )  | 9  |    |    |    |    |    | Υ  |    |          | i  | У   |                         |

| 1010                  | Α           | LF  | SUB |    |    | *  | :  |    |    |    |    | J  | Z  |    |          | i  | Z   |                         |

| 1011                  | В           | VT  | ESC |    |    | +  | ;  |    |    |    |    | K  | ]  |    |          | k  | {   |                         |

| 1100                  | С           | FF  | FS  |    |    | ,  | <  |    |    |    |    | L  | \  |    |          | 1  |     |                         |

| 1101                  | D           | CR  | GS  |    |    | 1  | 11 |    |    |    |    | М  | ]  |    |          | m  |     |                         |

| 1110                  | Е           | SO  | RS  |    |    |    | ^  |    |    |    |    | Ν  | ^2 |    |          | n  | ~   |                         |

| 1111                  | F           | SI  | US  |    |    | /  | ?  |    |    |    |    | 0  |    |    | <u> </u> | ٥  | DEL |                         |

- If IBM equipment implementing USASCII-8 is provided, the graphic | (Logical OR) will be used

- 2 If IBM equipment implementing USASCII-8 is provided, the graphic \( \tag{(Logical NOT) will be} used instead of A (Circumflex).

NOTE: Current activities in committees under the auspices of the United States of America Standards Institute may result in changes to the characters and/or structure of the eight-bit representation of USASCII devised by the Institute. Such changes may cause the eight-bit representation of USASCII implemented in System/360 (USASCII-8) to be different from a future USA Standard. Since a difference of this nature may eventually lead to a modification of System/360, it is recommended that users avoid: (1) operation with PSW bit 12 set to 1, and (2) the use of any sign codes in decimal data other than those preferred for EBCDIC.

# **Control Character Representations**

instead of ! (Exclamation Point).

|      |                            |     |                                |    |                        |               | •                               |

|------|----------------------------|-----|--------------------------------|----|------------------------|---------------|---------------------------------|

| NUL  | Null                       | DLE | Data Link Escape (CC)          | SP | Space                  | <             | Less Than                       |

| SOH  | Start of Heading (CC)      | DC1 | Device Control 1               | !  | Exclamation Point      | = ,           | Equals                          |

| STX  | Start of Text (CC)         | DC2 | Device Control 2               | Ī. | Logical OR             | >             | Greater Than                    |

| ETX  | End of Text (CC)           | DC3 | Device Control 3               | 11 | Quotation Marks        | ?             | Question Mark                   |

| EOT  | End of Transmission (CC)   | DC4 | Device Control 4               | #  | Number Sign            | @             | Commercial At                   |

| ENQ  | Enquiry (CC)               | NAK | Negative Acknowledge (CC)      | \$ | Dollar Sign            | [             | Opening Bracket                 |

| ACK  | Acknowledge (CC)           | SYN | Synchronous Idle (CC)          | %  | Percent                | Ň             | Reverse Slant                   |

| BEL  | Bell                       | ETB | End of Transmission Block (CC) | &  | Ampersand              | ]             | Closing Bracket                 |

| BS   | Backspace (FE)             | CAN | Cancel                         | 1  | Apostrophe             | · <b>A</b>    | Circumflex                      |

| HT   | Horizontal Tabulation (FE) | EM  | End of Medium                  | (  | Opening Parenthesis    | $\neg$        | Logical NOT                     |

| LF   | Line Feed (FE)             | SUB | Substitute                     | j  | Closing Parenthesis    |               | Underline                       |

| VT   | Vertical Tabulation (FE)   | ESC | Escape                         | *  | Asterisk               | $\overline{}$ | Grave Accent                    |

| FF   | Form Feed (FE)             | FS  | File Separator (IS)            | +  | Plus                   | {             | Opening Brace                   |

| CR   | Carriage Return (FE)       | GS  | Group Separator (IS)           |    | Comma                  | ì             | Vertical Line (This graphic is  |

| SO   | Shift Out                  | RS  | Record Separator (IS)          |    | Hyphen (Minus)         | '             | stylized to distinguish it from |

| SI   | Shift In                   | US  | Unit Separator (IS)            |    | Period (Decimal Point) |               | Logical OR)                     |

|      |                            | DEL | Delete                         | /  | Slant                  | }             | Closing Brace                   |

| (CC) | Communication Control      |     |                                | :  | Colon                  | ~             | Tilde                           |

| (FE) | Format Effector            |     |                                | ;  | Semicolon              |               |                                 |

| (IS) | Information Separator      |     |                                | •  |                        |               |                                 |

Special Graphic Characters

Figure 1-4. USASCII-8 Code

Figure 1-5. Instruction Formats

#### Legend:

R1, R2, and R3: 4-bit address of an LS register containing the first, second, and third operands, respectively.

M1: 4-bit mask used in some branching instructions.

X2: 4-bit address of an LS register containing the index value used in generating the effective second operand address.

12: 8-bit byte of immediate data (second operand).

L1 and L2: 4-bit length (up to 16 bytes) of first and second decimal VFL operands, respectively.

LL: 8-bit length field (up to 256 bytes) for logical VFL operands.

B1, B2: 4-bit address of a base register.

D1, D2: 12-bit displacement.

B1+D1 or B2+D2 = Effective storage operand address.

|                   |           |            |           | Double<br>C |           |            |           |            |           |            |            | Doubl      | eword<br>1 |            |            |            |

|-------------------|-----------|------------|-----------|-------------|-----------|------------|-----------|------------|-----------|------------|------------|------------|------------|------------|------------|------------|

|                   |           | Wo         | ord<br>)  |             |           | Wo         | ord<br>1  |            |           | Wo         | ord<br>2   |            |            | Wo         | ord<br>3   |            |

|                   |           | fword<br>0 | Hali      | word        |           | fword<br>2 |           | fword<br>3 | Half      | fword<br>4 |            | fword<br>5 |            | fword<br>6 | Half<br>7  | word       |

|                   | Byte<br>0 | Byte<br>1  | Byte<br>2 | Byte<br>3   | Byte<br>4 | Byte<br>5  | Byte<br>6 | Byte<br>7  | Byte<br>8 | Byte<br>9  | Byte<br>10 | Byte<br>11 | Byte<br>12 | Byte<br>13 | Byte<br>14 | Byte<br>15 |

|                   | ,         | -<br>      |           | 7           |           | 7          | ,         |            |           |            | ,          | ,          |            |            | ,          |            |

| Binary<br>Address | 00000     | 00001      | 00010     | 00011       | 00100     | 00101      | 00110     | 00111      | 01000     | 01001      | 01010      | 01011      | 01100      | 01101      | 01110      | 01111      |

Figure 1-6. Main Storage Integral Boundaries

Table 1-1. Fixed-Point Instructions

| Instruction       | Mne-<br>monic | Op<br>Code | Format | Operands         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                            | Program<br>Interruptions                      | Condition Code                                                                        |

|-------------------|---------------|------------|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------|

| Add               | Α.            | 5A         | RX     | R1<br>D2(X2, B2) | Algebraically add 2nd opr (in stg) to 1st opr (in GPR per R1) & place result into 1st opr location.  D(21) determines which word of doubleword from stg is 2nd opr: if 1, right word; if 0, left word.                                                                                                                                                                                                                                              | Prot (F) Adr Spec Fix-Pt Ovflo                | 0 : Sum = 0<br>1 : Sum < 0<br>2 : Sum > 0<br>3 : Overflow                             |

| Add               | AR            | 1A         | RR     | R1<br>R2         | Algebraically add 2nd opr (in GPR per R2) to 1st opr (in GPR per R1) & place result into 1st opr location.                                                                                                                                                                                                                                                                                                                                          | Fix-Pt Ovflo                                  | 0 : Sum = 0<br>1 : Sum < 0<br>2 : Sum > 0<br>3 : Overflow                             |

| Add Halfword      | АН            | 4A         | RX     | R1<br>D2(X2, B2) | Algebraically add halfword 2nd opr (in stg) to 1st opr (in GPR per R1) & place result into 1st opr location.  1. D(21) determines which word of doubleword from stg contains halfword 2nd opr: If 1, right word; if 0, left word.  2. D(22) determines which half of word is halfword 2nd opr: If 1, right half; if 0, left half.  3. Halfword 2nd opr is expanded to full word before addition by propagating sign bit through 16 high-order bits. | Prot (F)<br>Adr<br>Spec<br>Fix-Pt Ovflo       | 0 : Sum = 0<br>1 : Sum < 0<br>2 : Sum > 0<br>3 : Overflow                             |

| Add Logical       | AL            | 5E         | RX     | R1<br>D2(X2, B2) | Algebraically add 2nd opr (in stg) to 1st opr (in GPR per R1) & place result into 1st opr location.  1. D(21) determines which word of doubleword from stg is 2nd opr: if 1, right word; if 0, left word.  2. Sign bit of result is treated as high-order integer & is tested for carry to determine CC.                                                                                                                                            | Prot (F)<br>Adr<br>Spec                       | 0 : Sum = 0 (no carry) 1 : Sum ≠ 0 (no carry) 2 : Sum = 0 (carry) 3 : Sum ≠ 0 (carry) |

| Add Logical       | ALR           | 1E         | RR     | R1<br>R2         | Algebraically add 2nd opr (in GPR per R2) to 1st opr (in GPR per R1) & place result into 1st opr location.  Sign bit of result is treated as high-order integer & is tested for carry to determine CC.                                                                                                                                                                                                                                              | None                                          | 0 : Sum = 0 (no carry) 1 : Sum ≠ 0 (no carry) 2 : Sum = 0 (carry) 3 : Sum ≠ 0 (carry) |

| Compare           | С             | 59         | RX     | R1<br>D2(X2, B2) | Algebraically compare 1st opr (in GPR per R1) with 2nd opr (in stg) & set CC according to result.  D(21) determines which word of doubleword from stg is 2nd opr: if 1, right word; if 0, left word.                                                                                                                                                                                                                                                | Prot (F)<br>Adr<br>Spec                       | 0 : Opr 1 = Opr 2<br>1 : Opr 1 < Opr 2<br>2 : Opr 1 > Opr 2                           |

| Compare           | CR            | 19         | RR     | R1<br>R2         | Algebraically compare 1st opr (in GPR per R1) with 2nd opr (in GPR per R2) & set CC according to result.                                                                                                                                                                                                                                                                                                                                            | None                                          | 0 : Opr 1 = Opr 2<br>1 : Opr 1 < Opr 2<br>2 : Opr 1 > Opr 2                           |

| Compare Halfword  | СН            | 49         | RX     | R1<br>D2(X2, B2) | Algebraically compare 1st opr (in GPR per R1) with halfword 2nd opr (in stg) & set CC according to result.  1. D(21) determines which word of doubleword from stg contains halfword 2nd opr: if 1, right word; if 0, left word.  2. D(22) determines which half of word is halfword 2nd opr: if 1, right half; if 0, left half.  3. Halfword 2nd opr is expanded to full word before comparison by propagating sign bit through 16 high-order bits. | Prot (F)<br>Adr<br>Spec                       | 0: Opr 1 = Opr 2<br>1: Opr 1 < Opr 2<br>2: Opr 1 > Opr 2                              |

| Convert to Binary | СVВ           | 4F         | RX     | R1<br>D2(X2, B2) | Convert radix of 2nd opr (in stg) from decimal to binary & place result into 1st opr location (in GPR per R1).  1. 2nd opr is doubleword in packed format.  2. High-order word is converted first.  3. Max positive integer that can be converted is +2,147,483,647.  4. Max negative integer that can be converted is -2,147,483,648.                                                                                                              | Prot (F)<br>Adr<br>Spec<br>Data<br>Fix-Pt Div | Unchanged                                                                             |

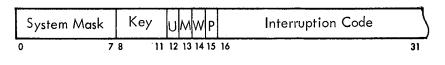

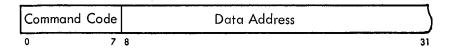

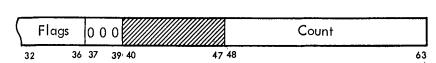

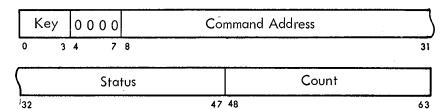

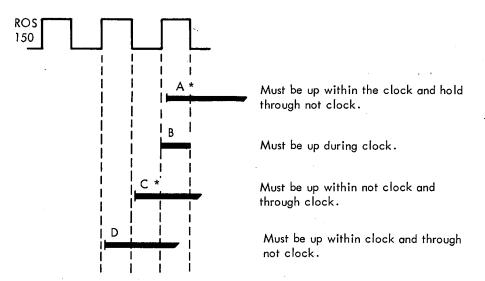

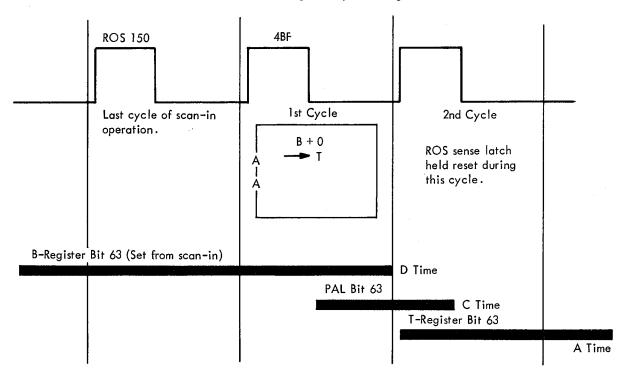

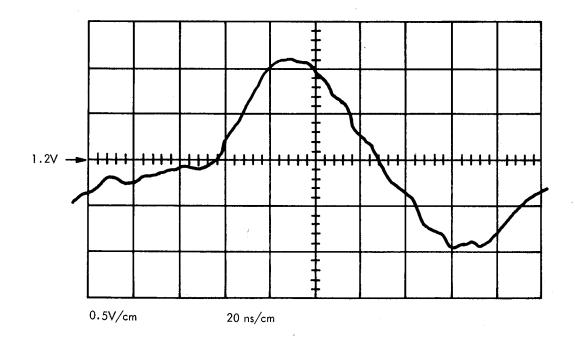

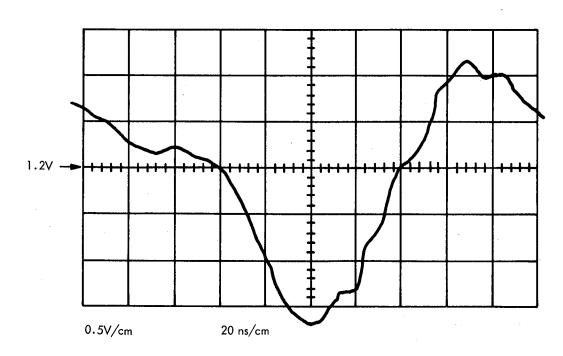

Table 1-1. Fixed-Point Instructions (Cont)